第六部分. 结论

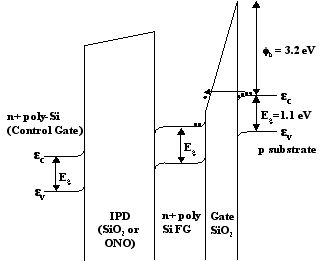

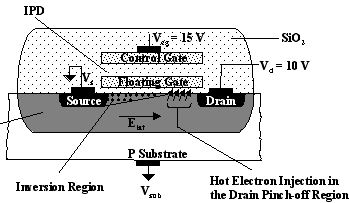

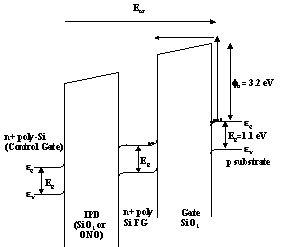

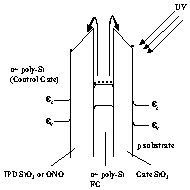

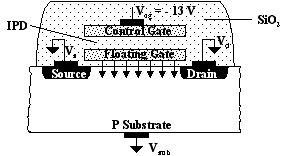

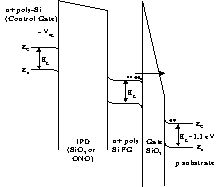

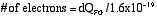

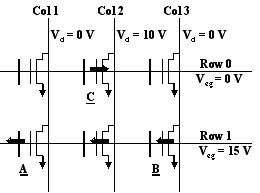

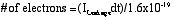

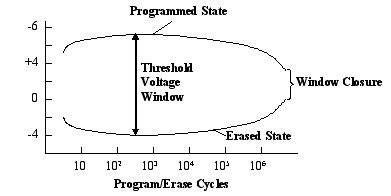

本文主要介绍了NVM的发展过程和技术概况。主要的编程手段有热载流子注入和FN隧道效应。在FN隧道效应中,门极氧化层厚度一般小于12nm,而在热电子注入中可以厚很多。两种典型的擦除机制为紫外照射和FN隧道效应,通常在UV EPROM中使用紫外照射擦除的方法,而在EEPROM和FLASH存储器中则使用了FN隧道效应擦除机制。紫外擦除所需的时间一般为10分钟而FN隧道效应擦除的时间根据控制门极和漏极上加载的电压强度不同仅为1ms到10ms。最快的编程机制是热电子注入,一般只需100ms。在此过程中,我们讨论了幸运电子模型,这个模型揭示了门电流是如何通过可能性模型来计算的过程。虽然注入的效率很低,但将热电子注入浮栅的过程是很快的,这是因为有外加强电场的作用。对于每个NVM器件来说,可靠性的问题都存在,而耐久力和数据保持力是最重要的两个问题。此外,在编程中和擦除中产生的干扰也是影响NVM可靠性的一个因素。

References

[1] Kahng, D. and Sze, S. M. (1967) A floating gate and its application to memory devices. Bell Systems Technical Journal. 46, 1283.

[2] Wegener, H. A. R, Lincoln, A. J., Pao, H. C., O\'Connell, M. R., and Oleksiak, R. E. (1967) The variable threshold transistor, a new electrically alterable, non-destructive read-only storage device. IEEE IEDM Technical Digest. 1.

[3] Wegener, H. A. R, Lincoln, A. J., Pao, H. C., O\'Connell, M. R., and Oleksiak, R. E. (1967) Metal-insulator-semiconductor transistor as a non-volatile storage element. International Electron Devices Meeting. (Abstracts). 58

[4] Frohman-Bentchkowsky, D. (1970) The metal-nitride-oxide-silicon (MNOS) transistor-characteristics and applications. Proceedings of IEEE. 58, 1207.

[5] Yatsuda, Y., Hagiwara, T., Kondo, R., Minami, S., and Itoh, Y. (1979) N-channel Si-gate MNOS device for high speed EAROM. Proceedings 10th Conference in Solid State Devices. 11.

[6] Suzuki, E., Hiraishi, H., Ishi, K., and Hayashi, Y. (1983) A low voltage alterable EEPROM with metal-oxide-nitride-oxide-semiconductor (MONOS) structure. IEEE Transactions on Electron Devices. ED-30, 122.

[7] Frohman-Bentchkowsky, D. (1974) FAMOS-A new semiconductor charge storage device. Solid State Electronics. 17, 517.

[8] Iizuka, H., Masuoka, F., Sato, T., and Ishikawa, M. (1976) Electrically alterable avalanche-injection type MOS read-only memory with stacked-gate structures. IEEE Transactions on Electron Devices. ED-23, 379.

[9] Masuoka, F., Asano, M., Iwahashi, H., and Komuro, T. (1984) A new flash EEPROM cell using triple poly-Si technology. IEEE IEDM Technical Digest. 464.

[10] Yeargain, J. and Kuo, K. (1981) A high density floating gate EEPROM cell. IEEE IEDM Technical Digest. 24.

[11] Guterman, D., Rimawi, I., Chiu, T., Halvorson, R., and McElroy, D. (1979) An electrically alterable nonvolatile memory cell using a floating gate structure. IEEE Transactions on Electron Devices. ED-26, 576.

[12] Lezlinger, M. and Snow, E. H. (1969) Fowler-Nordheim tunneling in thermally grown SiO2. Journal of Applied Physics. 40, 278.

[13] Tam, S., Ko, P., and Hu, C. (1984) Lucky-electron model of channel hot-electron injection in MOSFET\'s. IEEE Transactions on Electron Devices. ED-31, 1116.

[14] Takeda, E., Kume, H., Toyabe, T., and Asai, S. (1982) Submicrometer MOSFET structure for minimizing hot-carrier generation. IEEE Transactions on Electron Devices. ED-29, 611.

[15] Shockley, W. (1961) Problems related to p-n junctions in silicon. Solid-State Electronics. 2, 35.

[16] Harari, E. (1978) Dielectric breakdown in electrically stressed thin films of thermal SiO2. Journal of Applied Physics. 49, 2478.

[17] Modelli, A. and Ricco, B. (1984) Electric field and current dependence of SiO2 intrinsic breakdown. IEEE IEDM Technical Digest. 148.

[18] DiMaria, D. J. and Kerr, D. R. (1975) Interface effects and high conductivity in oxides grown from polycrystalline silicon. Applied Physics Letters. 27, 505.

[19] Faraone, L. (1986) Thermal SiO2 films on n+ polycrystalline silicon: Electrical conduction and breakdown. IEEE Transactions on Electron Devices. ED-33, 1785.

[20] Mori, S., Kaneko, Y., Arai, N., Ohshima, Y., Araki, H., Narita, K., Sakagami, E., and Yoshikawa, K. (1990) Reliability study of thin inter-poly dielectrics for nonvolatile memory application. Proceedings 1985 IEEE IRPS. 132.

[21] Aminzadeh, M. (1988) Conduction and charge trapping in polysilicon nitride-oxide-silicon structures under positive gate bias. IEEE Transactions on Electron Devices. ED-35, 205.

[22] Shiner, R. E. (1980) Data retention in EPROMs. Proceedings IRPS. 238.

[23] Mielke, N. (1983) New EPROM data-loss mechanisms. Proceedings IRPS. 106.

[24] Verma, G. and Mielke, N. (1988) Reliability aspects of ETOX based flash memories. IRPS Proceedings, 158

200字以内,仅用于支线交流,主线讨论请采用回复功能。