第五部分: NVM可靠性问题

NVM存储器单元有几个重要的功能性参数,用于评估单元的性能。这些参数基本可以分为两大类:耐久力和数据保持能力。为了更好的理解这些概念,我们有必要了解一些关于门氧化层,IPD的完整性知识。无论在EPROM, EEPROM还是Flash EEPROM中,影响器件可靠性的关键在于门氧化层和IPD的质量。

门氧化层主要的失效机制涉及到在热电子或者FN注入时由高电场引起的氧化层击穿和阱陷。有研究发现氧化层缺陷和硅氧踺断裂造成阱陷。氧化层击穿通常发生于通过单位面积的电荷数量(Qbd)超过一定水平之后,通常也和外加电场强度有关。Qbd是个工业标准电气性能测试,用于测量氧化层在高浓度Qbd情况下的表现。阱陷的定义是在对单元编程时造成的电子在氧化层中被困住的现象。这种现象改变了注入区域物理特性,因此,被转移到浮栅区的电子数量以及其间阈值电压也被改变。

此前已经提到过IPD,它通常用于隔绝浮栅区和其他区域,所以理论上它必须是无缺陷以防止漏电流的产生。由于浮栅是由多晶硅构成的,通常是在IPD生长工艺过程中被氧化的。氧化的过程导致在grain 边缘增强从而改变了多晶硅表面的物理结构,形成了小隆起状表面。这些表面的不平整导致了局部电场的变化,引发了高漏电流。影响IPD质量的其中一个因素是多晶硅层的参杂和多晶硅沉淀,氧化时的温度控制。多种绝缘材料并用,可以减少缺陷密度和提高电场均匀度如氧-氮-氧现在被广泛应用于IPD中以防止漏电流的产生。在此材料中,浮栅电子被氮氧层困住,从而形成与漏电流反向的电场,进一步减小漏电流的扩大。通常ONO层厚度为5 - 10 nm(底层氧化), 20 nm(氮层), 3 nm(顶层氧化)。底层氧化是在浮栅区上面,而顶层氧化位于控制门极下面。

图十四,由于表面不平整引发的IPD 漏电流

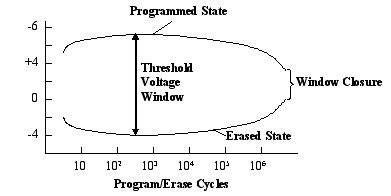

Va. 耐久力特性

耐久力特性表现于存储器的阈值电压区间,它与编程次数有密切的关系,如图十五所示。NVM可以被编程和擦除直到氧化层被破坏。这也意味着NVM有效的可编程次数是有限的,举例来说大部分商用EEPROM产品可以保证106 有效编程次数。此情况下氧化层的破坏通常被称为氧化层的降级,而一个存储器可以经受的最大编程次数被称为耐久力。阈值电压窗口关闭通常发生在两者值(高电平与低电平状态)太小以至不能被明显区分。这种现象归咎于电子被氧化层中原有的电子阱陷所困住无法再移动,另有实验证明阱陷是在对单元编程或者擦除过程中氧化层两端加载的高电场所产生的。因此,门氧化层的质量对于器件耐久力尤其重要。

图十五,典型的EEPROM单元阈值电压窗口关闭

Vb. 数据保持能力特性

当一个NVM单元无法保持浮栅中的电荷量时,我们称之为数据保持能力的丧失。数据保持能力是衡量一个NVM存储器单元在无电源供应情况下可以保持数据的时间。在浮栅型存储器中,存储在浮栅区的电荷会通过门氧化层和IPD流失。由自由电子(离子)移动和氧化层中缺陷所产生的漏电流,会导致单元阈值电压的改变。不同的电子流失方式有:温度引起的电离,电子中和,由于正离子污染引发的流失。为了提高单元的保持数据能力,人们采用了不同的手段来提高门氧化层和IPD的质量。

数据保持能力可以用估计生命周期来量化,当电荷流失发生时,单元的阈值电压变化如下:

其中dQFG, CFG, 和 dVT 分别为浮栅区电荷变化,浮栅电容量和单元阈值电压。等式9展示了流失电子的数量,等式10则展示了流失电子数量和形成的漏电流的关系以及保持时间。

对于典型的 CFG = 30 fF 和 VT 变化为3 V,从浮栅区到控制门区电子流失的数量 大约为 5.6x105个。表格 1 展示了保持时间 dt,对于不同的 ILeakage 相关与5.6x105 电子流失或相当于3 V VT变化。

Leakage Current, ILeakage (A) Retention Time, dt (Years)

1x10-20 0.28

5x10-21 0.56

1x10-21 2.84

5x10-22 5.68

2.85x10-22 10

表格一,数据保持时间与ILeakage

由表一可以看出普通的NVM阈值电压降低3V,漏电流为2.85x10-22 A的情况下总共需要10年。

Vc存储器干扰

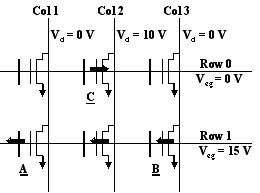

大规模的在生产中使用NVM需要他们具有10年以上的数据保持能力。一个存储器单元阵列在编程和擦除中经受stress被称为干扰。具体而言有四种:dc erase, dc program, program disturb,和read disturb。在编程过程中最常见的两种干扰是dc program和program disturb,在擦除过程中最常见的则是dc erase,最后在读过程中的干扰被称为read disturb。图十六展示了一个存储器单元阵列电路图,它将被用于解释干扰现象。

图十六,用于解释干扰现象的电路图

在上图中,存储器单元阵列的列连接着每个单元的漏极,(COL 1, COL 2, and COL 3) 被称为位线,而阵列的行连接着每个单元的控制门极 (ROW 0 and ROW 1) 被称为字线。在前面关于热电子注入的讨论中已经说过,在对存储器编程时需要同时在位线和字线加载电压。

下面来讨论这四种不同的干扰:

1) DC Erase: 这种类型的干扰通常发生在已经被编程的单元(Cell A)。那些在与被编程的单元在同一条字线 (ROW 1) 的单元正在被编程(COL 2 and ROW 1)。在此期间ROW 1 被加载一个高电压15 V,由此产生的一个高电场出现在IPD的两侧。这个电压可能导致电子从浮栅区移动到控制门区,结果是电荷流失造成单元的阈值电压减小。

2) DC Program: 也被称为gate disturb,发生于当未被编程的或者已擦除的单元 (Cell B)。这些未编程的单元与正在被编程的单元在同一字线上 (ROW 1) 。这些单元只有很少量的电子在浮栅中,因此他们的阈值电压是低电平的。当ROW1加载15V时,通过门极氧化层的电场变得被得很强,这一电场可能导致电子进入浮栅区从而提高阈值电压。这种情况下,我们称之为软编程。

3) Program Disturb: 通常也成为drain-disturb,只发生于被编程过的单元。一个被编程过的单元 (Cell C) 与正在被编程的单元 (COL 2 和 ROW 1)共享一条位线。在它的浮栅/漏极区有一个高电场存在。这一高电场导致了电子从浮栅区移向漏极区从而导致阈值电压减小。

4) Read Disturb: 这种干扰机制发生于与正在被读的单元共享一条字线的擦除过的单元。共享的字线上的擦除电压为5V,被选中的单元漏极偏置为1V,未选择单元的源极,漏极,和substrate均为0V。