曾经了解过,但是拆机的7010太香了 就没去深入研究过(捂脸

说实在的 FPGA/CPLD对于我而言 比较鸡肋 现在MCU性能不低 而且接口日益集成和统一 一般爱好者都找不到使用的机会 我曾经想在运动控制中使用 后来一想 DIR/STEP接口本身就该淘汰了 至于并行显示或者高速采集接口之类 我也没有多少兴趣

不过 廉价是王道 如果MCU+CPLD够便宜的话 也不是不可以玩玩 比如AGM的AG32VF系列 集成了一个32位RISCV MCU和2k LEs的CPLD 价格与一般的同档次MCU差别不大 TB网页直接说了类似"卷到死"的话

目前该系列有AG32VF103/303/407 不过 其实从价格就可以看出来 区别其实只在引脚数量上 有48/64/100三种 内核都是一样的 邦定不同罢了 flash应该是另一个DIE 有256k/512k/1M (CPLD应该要用最后100-148k) RAM都是128k CPLD另有4k 主频248M 超频据说能到300多M

需要注意的是ADC/DAC是要占用LEs的 官方提供了verilog代码 满通道全用最多要占到1.5k左右 如果要搞一些自己的电路 估计要放弃一些

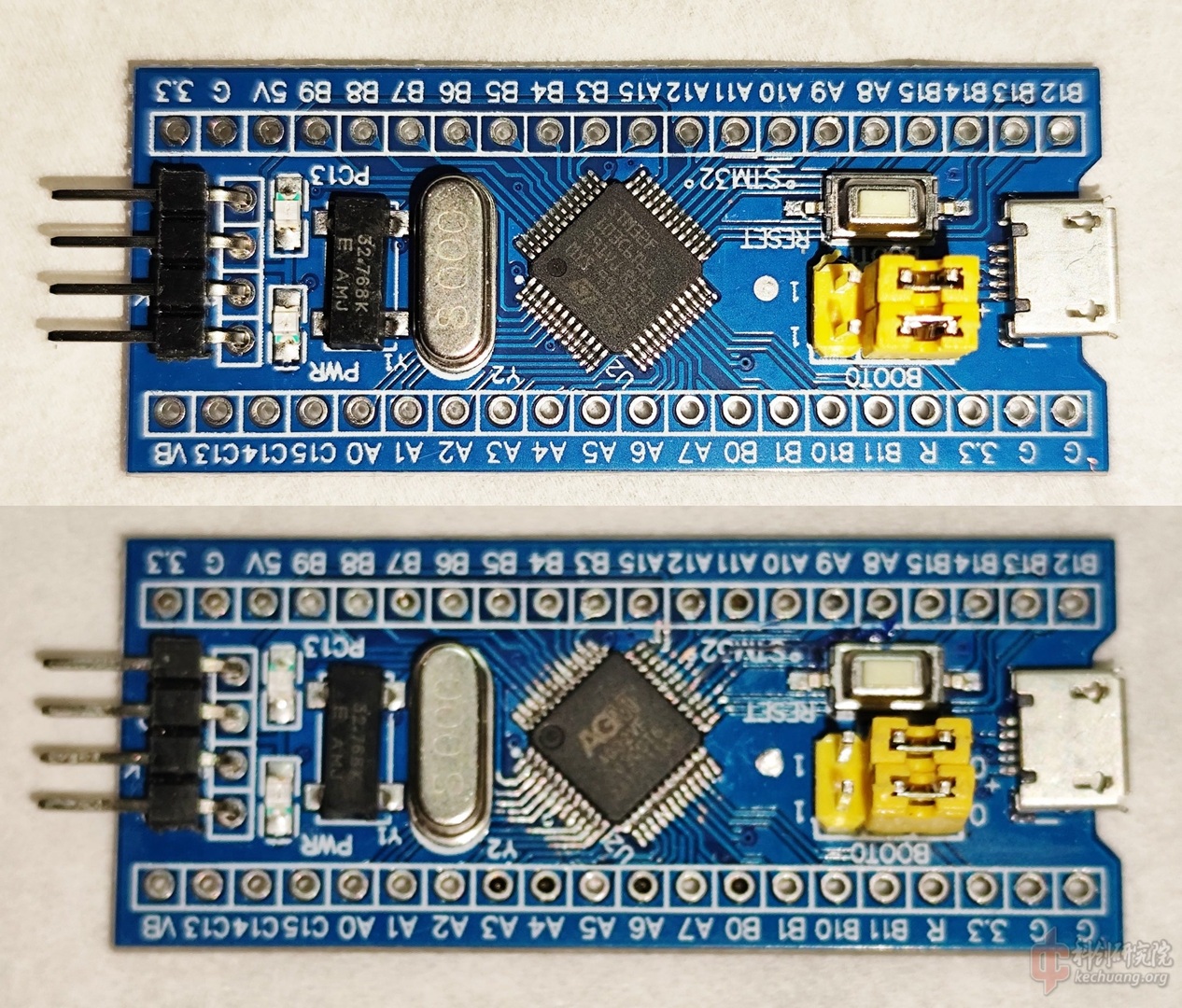

官方开发板一向贵 不过 反正不是引脚兼容么 也可以用普通的STM32开发板移花接木 于是3块钱买了块小蓝丸f103国产假冒芯片的开发板 ... 我有个pen 有个apple 于是 pineapple也有了

需要注意的是stm32f103c的35脚是地 ag32vf103c/303c的35脚是IO 稳妥起见要划断铜箔 开发时候为了兼容性 不用那个脚

官方提供的开发包可以在https://github.com/AGMCU/AGMCU找到 不过 没有源代码 要在release里面找

AGM提供的文档非常的简陋 但是有了开发包 里面还有例子 基本也就没有太多问题了 开发包基于platformIO

烧录可以通过串口(Boot0接高) 或者使用jlink/usb-bluster/openocd 当然最方便是用openocd了 在开发包里面搜索一下一个叫"agrv2k.cfg"的文件 就是openocd的脚本 在最前面加上几行

Bashset ADAPTER cmsis-dap

set CONNECT_UNDER_RESET 1

set ADAPTER_SPEED 1000就可以用"openocd -f argv2k.cfg"来连接 (硬件上要提供3.3V电压 连上SWIO/SWCLK)

BashOpen On-Chip Debugger 0.12.0+dev-03761-g5b5e10502 (2024-03-20-10:51)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : Using speed 1000 KHz

Info : CMSIS-DAP: SWD supported

Info : CMSIS-DAP: FW Version = 1.0

Info : CMSIS-DAP: Interface Initialised (SWD)

Info : SWCLK/TCK = 1 SWDIO/TMS = 1 TDI = 0 TDO = 0 nTRST = 0 nRESET = 0

Info : Connecting under reset

Info : CMSIS-DAP: Interface ready

Info : clock speed 1000 kHz

Info : SWD DPIDR 0x2ba01477

Info : [cpu] datacount=1 progbufsize=16

Info : [cpu] Disabling abstract command reads from CSRs.

Info : [cpu] Disabling abstract command writes to CSRs.

Info : [cpu] Examined RISC-V core

Info : [cpu] XLEN=32, misa=0x40801125

[cpu] Target successfully examined.

Info : [cpu] Examination succeed

Info : starting gdb server for cpu on 3333

Info : Listening on port 3333 for gdb connections

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : accepting 'telnet' connection on tcp/4444

Info : device id = 0x40200001

Info : agrv2k.FLASH size = 256kbytes用"flash banks"命令看看flash的信息 (flash probe ? 或者 flash info ? 可以看到更多没有多少意义的信息)

Bash> flash banks

#0 : agrv2k.FLASH (agrv) at 0x80000000, size 0x00040000, buswidth 0, chipwidth 0

#1 : agrv2k.ROM (agrv) at 0x00010000, size 0x00002000, buswidth 0, chipwidth 0然后还一种方式 使用USB口烧录 需要在开发包里面找一个叫"dfu_usb.bin"的文件 烧录进去

Bash> flash write_image dfu_usb.bin 0x80000000

用USB线接入 电脑会报道找个COM口 在开发包里面找一个叫"agrv32flash.exe"的程序 就可以通过这个USB COM口烧录程序了 不必每次再连DAPLINK 但是程序就不能放在0x80000000处了 好像要放在0x80008000

Bash> agrv32flash.exe COM16 agrv32flash 1.0.0 Initializing device... I..I Done Interface serial_w32: 57600 8E1 Version : 0x20 Option 1 : 0x5a Option 2 : 0xa5 Device : 0x40200001 (AGM32RV40xxx) - RAM : 0x20000000 128KiB - Flash : 0x80000000 256KB (size first sector: 1x4096) - Option RAM : 0x81000000 128B - System RAM : 0x10000 8KiB

因为目前暂时没有什么想法 找不到CPLD应用方向 验证了一下芯片没坏 可以访问 就停手了

[修改于 10个月16天前 - 2024/06/05 17:16:36]

开眼了,很多年没玩这些,这几年变化真快,居然有与STM32管脚兼容的CPLD,很好啊,做小东西方便了。

假期做了更多零碎尝试 这里就不多细说 仅做总结

python环境是必须的 而且要更新到位 开发包里面使用了一些多类型检查方面的新语法 我版本有些低了 只好自己改了下

MCU开发环境基于platformio 安装很简单 用pip install platformio即可 之后再安装开发包即可 platformio完全可以通过pio命令完成所有需要的操作

目前感觉开发包也有很多问题 比如需要手动在安装好的AgRV_pio\packages\tool-agrv_logic目录下 增加一个package.json文件 不然platformio不认这个目录 后面使用pio会遇到问题

JavaScript{

"name": "tool-agrv_logic",

"version": "1.0.0",

"description": "tool-agrv_logic",

"keywords": [

"tools",

"logic"

],

"system": [

"windows_amd64"

]

}vscode不是必须的 我不喜vscode 喜用eclipse 在工程的主目录下 使用命令pio init --ide eclipse就可以用eclipse打开工程了

BashD:\WORK\custom_ip>pio init --ide eclipse

Resolving debug dependencies...

Project diretory: D:\WORK\custom_ip

PlatformIO Core version: 6.1.15

AgRV Core version: 1.5.0

Already up-to-date.

Updating metadata for the eclipse IDE...

Project has been successfully updated!但是除了build之类的通用target 还有一些和CPLD方面的target 需要通过命令pio run -t <target>手动执行 也可以手动加到eclipse项目的build target 其中最有用的是prelogic preip logic这三个 建议通过eclipse写/烧MCU代码 CPLD方面还是手动操作就行 反正也需要通过Quartus II和Supra来开发 和eclipse么有关系

Bashdebug Custom batch Create Batch Create Batch bitstream agm_custom_ip_debug_batch.bin

debug Custom batch_upload Upload Batch Upload Batch bitstream agm_custom_ip_debug_batch.bin

debug Custom gc Garbage Clean Cleaning up build leftover garbages

debug Custom logic Upload LOGIC Programming LOGIC bitstream top.bin

debug Custom logic_clean Clean LOGIC Cleaning up logic environment

debug Custom preip Prepare IP Preparing LOGIC IP compilation project top

debug Custom unlock Unlock Flash Setting Flash read unprotect (Unlock)

debug Custom wipe Wipe Flash Wiping Flash to Factory Settings

debug Platform upload Upload

top Custom batch Create Batch Create Batch bitstream agm_custom_ip_top_batch.bin

top Custom batch_upload Upload Batch Upload Batch bitstream agm_custom_ip_top_batch.bin

top Custom gc Garbage Clean Cleaning up build leftover garbages

top Custom logic Upload LOGIC Programming LOGIC bitstream top.bin

top Custom logic_clean Clean LOGIC Cleaning up logic environment

top Custom prelogic Prepare LOGIC Preparing LOGIC compilation project top

top Custom unlock Unlock Flash Setting Flash read unprotect (Unlock)

top Custom wipe Wipe Flash Wiping Flash to Factory Settings

top Platform upload Upload大概的说 开发设计包括3个部分 MCU的代码 CPLD的设计 以及.ve引脚设计 流程大概如下

首先需要改写platformio.ini 确定board/board_logic.ve/board_logic.device/ip_name/logic_dir等关键参数

编写board_logic.ve 内容包括时钟的设计 以及MCU/CPLD/外部Pin三方的互联 值得注意的是 开发包中例子的.ve文件都是针对100引脚的 32/48/64引脚的 都需要自己重新编写

使用pio run -e <环境> -t prelogic来生成CPLD工程 此外 它还会根据.ve文件 生成MCU开发需要的时钟方面的.hx头文件 以及引脚关联有关的其他文件 所以这步即使是不做CPLD开发 也是必须的

然后就可以使用各种IDE来开发MCU程序了 CPLD方面使用Quartus II来设计 产生.vo文件给Supra使用 需要注意的是Quartus II需要使用正式版 web/lite版本是不行的 官网文档有明确提出这点 此外需要加上cyclone IV和MAX系列的设备包 (仿altera cyclone IV很正常 国内早就实现假货满天飞了 但是为啥要加MAX系列设备包我不太理解 但是也加了)

最后都需要Supra的compile功能来完成布线 产生.bin文件 即使不做CPLD 引脚映射也需要的

烧录可以用openocd 可以先烧布线 在flash的最后102400 bytes 然后再烧MCU部分 一般从0x80000000开始

MCU部分 我一直疑惑这是一个固化的RISCV软核 还是一个真正的硬核 但是官网找不到解答 但是其更高端产品是确定带arm硬核的 它提供了类似systick的MTime 以及类似stm32f103的高级定时器 常用的SPI/I2C/UART都有 但是高级应用方面稍有些简陋

值得一提的是它的GPIO 除了仍然要注意和SPI/I2C/UART/Timer等的共用冲突之外 上拉下拉开漏都不能简单通过API实现 上拉下拉需要在.asf文件中通过命令实现 开漏需要在.ve文件中指定

有意思的是 GPIO的位掩码非常具有特色 我之前遇到的 假如仅仅需要修改GPIO某些引脚 要么通过读-修改-写的方式 要么通过arm的置位/清除寄存器或者位带操作 而这里是通过不同的访问地址来实现 举个例子 AG32VF的GPIO1 有8个位 假如只要修改第2第5位 就使用GPIO1的data寄存器地址 加上偏移0b100100来读写

CPLD方面 2k的LEs说大不大 实现不了几个复杂的接口 但是说小也不小 甚至可以搭NIOS软核了 而硬IP方面 只有一个PLL 4个Mem9K 样例里面有一些有用的代码 比如ahb2qspi.v ahb2ram.v ram2ahb.v等等 Quartus自带一些有意思的软核 但我还没有实验

MCU 固有外设 CPLD 三方 可以通过AHB(还支持4路DMA) 以寄存器方式 或者Mem9K搭建的buffer互动 CPLD可主可从 也可以通过GPIO等外设连接的方式使用 除了PLL CPLD还可使用MCU时钟或者总线时钟 可以引发4条MCU外部中断线 ... 嗯 可以从下图大概看出 可以和MCU/IO哪些地方互连 (不过 也可能不是所有信号都能用 毕竟有些信号.ve文件可能不支持)

200字以内,仅用于支线交流,主线讨论请采用回复功能。