等着看下使用情况

最近买了一个nanoVNA玩玩,还没到货,但是发现没有比较简明的文章来梳理它的工作原理。所以整理编辑了一些相关的资料,分享给使用它的或者对它感兴趣的爱好者。对于仪器的更深入的理解有助于更好地使用仪器,获得更好的测试精度和使用体验。nanoVAN是一个有意思的仪器,它的设计思路是很精巧的,值得分享给大家。我目前也不是射频或数字信号方面的专家,所以有问题欢迎指出,太难的问题我也没法回答。

关于本文:着重于定性上理解它的工作原理,默认读者具有一定的射频基础,大致了解矢量网络分析的原理。未被提及的技术基础有:S参数,定向电桥,傅里叶变换,数字信号处理。

nanoVNA具有不同的硬件版本。我所购买的硬件应该是国内开发者hugen(http://bbs.38hot.net/thread-756047-1-1.html)发布的,在淘宝购入。而原版本的开发者为日本edy555(https://twitter.com/edy555)。他在网上开源了NanoVNA的相关电路图和软件(GitHub)。其实整个系统的架构并不少见,但是整合开源至此等程度的似乎不多。

首先,简单地提一下VNA。图来自《微波器件测量手册》。里面有四个关键的装置:驱动用的信号源,定向耦合器,混频器和本地振荡信号。其中源用来激励网络,定向耦合器用来分离S11回波和注入激励,混频器用来进行下变频,本地振荡器则是下变频的信号源。

而nanoVNA用300元实现了最高到900MHz的网络分析,实现了这四个元件。 下变频后,需要对本振后的中频信号进行分析,从而就能实现对网络参数的解算。和很多现代VNA一样,得益于高性能的数字电路,中频信号被直接送入ADC采样并进行数字信号处理。图片来自安捷伦。

所以混频后和大部分的混合电路设计一样,进入到抗混叠然后被ADC直采。其中抗混叠低通滤波器同时又是中频信号的低通滤波器,来分离出差频信号。在全功能的VNA中,为了动态范围和精度的考虑,低通还可以换成窄带的带通滤波器,来精准分析某一个差频信号。而在nanoVNA这类的设计中,为了节约成本减少复杂度,窄带的带通滤波器可以直接以离散数字滤波器的方式来实现。在这点上和SDR是一致的。当然这些都是系统工程,VNA的设计复杂异常。

在有了以上的基础理解以后,就可以进入到nanoVNA的架构分析了。此图来自日本的原本开发者的Github开源文件。这个图的版本可能比较新了,和国内版的不同的地方是,他添加了VCTVXO,压控温度补偿晶振。估计是通过STM32的内置温度传感器和DAC来进行温度补偿,从而达到更好的温度稳定性。和刚刚提到的基础架构一样,里面有三个混频器,是最简单的那种。

Si5351的真身是一个时钟产生器,它负责发生方波的时钟信号。这就是nanoVNA廉价的秘密。通过方波的三次谐波(甚至五次谐波),只有200MHz的时钟能产生600MHz的谐波。通过对它的寄存器的一些操作,能直接使它工作到300MHz。所以这么多的倍频下,时钟的稳定性还是有一定的影响的。时钟信号通过电阻网络分离出以路参考信号,一路驱动信号,驱动一个电桥。而所有的信号再和它产生的一个中频信号混合进入到一个声卡芯片。当然进入前有一个一阶低通滤波器和一个交流耦合电容。

比较有意思的一点是当时我没想明白整个系统是如何启动的,毕竟STM32的CLK信号来自5351,查了手册才明白它能被编程上电默认配置来专门启动MCU这一类的设备,从而可以节约一个晶振。

原作者并没有在他的开源文件中提及信号部分的设计原理。然而这一部分其实才是整个VNA的精华所在。不过有一个不错的视频稍微深入讲述了这个原理。来自Hamradio 2018 FA-VA5 presentation-UK(https://www.youtube.com/watch?v=X8Z7veGV57o),对FA-VA5这个天线分析仪的演讲。它同样是低成本网络分析设备,使用了和nanoVNA一样的架构,甚至一样的时钟芯片。不同的是它直接采用开关混频,据他说三阶谐波的成分会更大。

我从他的视频中截图了来说明它的工作原理。上方是一个方波的傅里叶展开,可以看见有大量的谐波成分。表格中为每个成分相互混频后的展开结果。而所有成分中能落入低通滤波器的只有中间这几个。由于是交流耦合的,所以不存在第一个直流信号。所以只有本振和激励的一阶三阶的差频能被ADC采样到。当然理论上5阶也行,不过考虑到信号幅度可能并不适合。然后只要进行数字处理,就能很轻松地提取出这个差频相对参考差频的相位和幅度。经过一系列的校准算法就能获得不错的数据了。谐波拓展原理也限制了它对一些有源器件的测试能力,基波可能导致放大器直接饱和或者非线性。如果能添加一个带通滤波器就能获得更加精准的测试结果。

以上就是一些对于nanoVNA原理性的简单分析了。

[修改于 4年11个月前 - 2020/05/19 15:20:32]

如果没记错。STM32可以先由内部RC振荡器作为时钟源,启动外设后再切换为外部时钟源

对Nano关注不多,500M和900M版本总不能也是NE602做混频器吧

如果没记错。STM32可以先由内部RC振荡器作为时钟源,启动外设后再切换为外部时钟源对Nano关注不...

有可能的,这样就不用额外对时钟源编程了。sa612就是同时混频了多个倍频的,应该是超频使用了,所以性能会有所劣化。不过后期都靠软件补偿了。没有500M和900M版本,他们都是在一个版本里面完成的呢。

恭喜楼主写出了外文机翻的风格。

去年有人拿了一个399元版的nanoVNA给我评估,看了一下,设计方面增加了一片ADF4350(也可能是4351,记不清了),频率范围有较大扩展(现在扩到了4G)。射频部分在开源网分中算是做得比较认真的。

有的扩展好像是中国人发挥聪明才智做的,跟原版略有区别。

实测指标还可以,由于电路环节少,漂移反而比较小,回损也不错。虽然没有ALC设计,但信号源从1M~2GHz似乎都能稳至-10dBm附近,波动只有2dB左右,可以说相当漂亮了。

不是很理解stm32上的DAC为什么要连接到VCTCXO上,这不是一个无源晶振吗?

引用18571547566发表于8楼的内容不是很理解stm32上的DAC为什么要连接到VCTCXO上,这不是一个无源晶振吗?

前面的VC 应该是压控的意思 Voltage-Control

此外STM32启动都是先使用内部RC的(不是可以而是肯定 包括从休眠中醒来) 直到程序再次指定以外部时钟或晶振

此外 我对STM32f072居然使用压控频率源感到很费解 USB可是需要相当稳定和准确的时钟的 查了一下才发现 它居然内部带了个USB专用的48M振荡器 这可是相当少见的 而且也不容易实现的

因为实际已经有内部准确48M时钟 此系统还采用外部时钟源 应该不是为了省去晶振 估计有同步方面的原因(可能是I2S总线的原因)

前面的VC 应该是压控的意思 Voltage-Control此外STM32启动都是先使用内部RC的(...

这有啥奇怪的,他的VCTCXO是作为主参考用的,机器出厂要做频率校准,就调调DAC就行了。

真是把性能压榨到极致的设计。时钟源用寄生频率来扩展频率已经够独特的了。SA612我印象也就跑个3,5百兆吧,居然用到了900M。好奇其电桥是咋做的,如果是简单的电阻桥,那么reflection混频器的共模抵抗能力还是不错的。当年我自己做着VNA玩,就是在电桥部分做伤了,做了极为复杂的,用了各种磁性材料的桥,结果发现大量在卖的VNA根本不搞那么复杂,就一个简单惠斯通电桥完事,完全不考虑用磁材来抑制共模,提高定向性之类的指标,性能居然也不错。我记得SA602的输入饱和点(好像是IP3吧)指标也不怎么样,输入稍微大点就会导致输出压缩。如果还用到寄生频率,那么如何避免基带频率能量过高导致SA602非线性可能也得考虑。

真是把性能压榨到极致的设计。时钟源用寄生频率来扩展频率已经够独特的了。SA612我印象也就跑个3,5...

就这几个电阻啦。这个就是玩具级别的,大差不差就行了呢,应该不会考虑这么周全。

真是把性能压榨到极致的设计。时钟源用寄生频率来扩展频率已经够独特的了。SA612我印象也就跑个3,5...

现在应该没人用磁性材料了吧,磁性材料是有幅度相关的非线性的,没有用电阻好,而且生产组装都太麻烦。低频用电阻,高频用定耦,已经成为固定模式了。传统定耦虽然频率低不了,但主通路的反射极小,因此在他前面放电阻桥是可以的,高频的时候旁路一下就行了。

实际上随着高频差分器件的发展,20G甚至40G以下都可以用电桥,电桥可以变化各种花样,只要有一个对角能搞成差分就行了。

定耦就更邪乎了,整一堆电阻搞集总分布相结合,也能一个管完低频到几十G。

这有啥奇怪的,他的VCTCXO是作为主参考用的,机器出厂要做频率校准,就调调DAC就行了。

但是对STM32而言 如非需要I2S上的频率精度 用这个时钟并无必要

感觉是你误解我观点的重点

现在应该没人用磁性材料了吧,磁性材料是有幅度相关的非线性的,没有用电阻好,而且生产组装都太麻烦。低频...

K的一些新矢网想fieldFox什么的,用的有源电桥,ADI也有那个ADL5960的芯片预发布。K的主流机器使用定耦应该是能做到10MHz的低频的,但是好像没注意到过有用双桥切换的网分型号。

看来是的,CPU时钟锁相并无绝对必要,或许只是设计师突发奇想吧。

在CPU内部还要对SA602的输出做二次数字混频+窄带通滤波,并进行I-Q测量。CPU的主频如果和射频同步,那么二次数字混频会极为简化。就按CPU时钟节律生成本振,与一中频相乘积分即可。

在CPU内部还要对SA602的输出做二次数字混频+窄带通滤波,并进行I-Q测量。CPU的主频如果和射...

CPU不是FPGA,这程序恐怕不好写,我没看他的源码,直觉不会如此,也没有必要。简化的算法只需要4倍采样,DDC是允许偏差的,不需要同步。

K的一些新矢网想fieldFox什么的,用的有源电桥,ADI也有那个ADL5960的芯片预发布。K的...

那就是电阻桥,别发明耸人听闻的名词,我在另一个帖子里面详细讲解过。

看来是的,CPU时钟锁相并无绝对必要,或许只是设计师突发奇想吧。

哈哈哈,我当年就是这么做的,FPGA+同步时钟。CPU不做任何运算,只负责从FPGA到上位机之间来回搬移翻译。换做CPU来做二次中频的话,实时性如果要求不高,CPU只负责按照同步节律采样即可。等数据采集全了再做数字相关算法。

没做过用CPU做二次中频运算。粗想起来,如果二次中频时钟和射频时钟ppm相差太大并且不稳定的话,若中频带宽太窄(对应相关运算时间较长),那么ppm会带来误差,补偿这个误差还需要费点麻烦。

现在应该没人用磁性材料了吧,磁性材料是有幅度相关的非线性的,没有用电阻好,而且生产组装都太麻烦。低频...

我当年搞出来的,底噪到负60多dB,再也下不去了。当时觉得是某个地方线性不佳,做校准时会残留误差,导致校准后底噪不行。因为如果不校准,只做重复测量,那么误差极小,有负100dB那个量级。怀疑非线性的来源可能是混频器信号幅度过大,混频器后的变压器有磁性材料,电桥有磁性材料,混频器到ADC之间有运放,可能都会贡献非线性。没进一步检查了。我做东西有个坏毛病,就是做着做着觉得把它基本搞懂了就会突然失去兴趣。当时的个人条件也不允许花很多时间鼓捣,这玩意也内卷得厉害,网上能买到很多指标凑合又便宜的,就没动力往商品化方向努力了。

哈哈哈,我当年就是这么做的,FPGA+同步时钟。CPU不做任何运算,只负责从FPGA到上位机之间来回...

你用的相关算法求时间差吗?应该直接矢量内积求相位差就行了吧,相关算法的抖动怎么样?

你用的相关算法求时间差吗?应该直接矢量内积求相位差就行了吧,相关算法的抖动怎么样?

算是内积。就是用FPGA运算出来的二本振SIN和COS两个三角函数信号,分别与refr,refl,through三个一中频信号做乘加,积分得到三个IQ,也就是你说的内积。

我明白你的意思,如果二本振与一中频信号不同源,没关系,因为本质上不是测量二本振与一中频的关系,而是测量三个一中频的相互关系。只要三个一中频是同时被测量的,那么他们相对于二本振的关系相当于三个常数,在运算三个一中频的相互关系时被消掉了。

然而如果二本振与中射频部分ppm相差太大,积分的时间又比较长且不走运的话,是有可能恰好积分周期处于两个时钟系统的差频上的,在某些情况下,三个一中频信号积分出来的东西都很小甚至是0,此时三个信号都不显著,就无法运算出可信的结果了。这里的关键是差频与积分周期的关系。如果射频部分和数字部分的时钟都是来自晶振的话,应该问题不大。因为在整个内积长度内两者相位滑动不大。但是如果CPU是用内部RC振荡器的话,可能会相互滑动很多相位,就不好说了。

反射校准后底噪-60?已经可以了嘛。

主要是我在单位用的都是负一百dB的量级,标称甚至有到负140dB的。即使随随便便测量一下都能达到负八九十dB。有这样的标杆在,自己diy的就拿不上台面了。

主要是我在单位用的都是负一百dB的量级,标称甚至有到负140dB的。即使随随便便测量一下都能达到负八...

反射一般就测到-30就够了,要-100有何意义呢,不知道你说的是不是同一个东西,不是S21。当然,只要仪器足够稳定,校准后的反射噪底到-100没啥问题,然而毫无意义。

举个例子可能更容易说明我要说的。

假设一中频是个1MHz正弦波。二本振也是个1MHz正弦波。两个向量完全相关,两者做内积,积分时间越长,积出来的东西越大。

但是假设现在一中频与二本振不同源了,假设二本振是RC振荡出来的,不稳定,现在是1.01MHz,那么以一个1MHz和1.01MHz做内积,积分出来的东西可不是随着时间单调增长的,而是会先慢慢增长,然后又慢慢下降,然后又回到零,然后向负方向增长。。。会以两者的差频来涨缩。如果中频带宽取得也不是很走运,是有可能刚好积分到零附近时结束内积的。那就倒霉了。

反射一般就测到-30就够了,要-100有何意义呢,不知道你说的是不是同一个东西,不是S21。当然,只...

是相当于S11。做校准时,load做最后一步,做完后不拧下来,直接测load,就有-60dB。我期望是负80到100dB。

如果我反复在一个单一频点测同一个DUT,那么各个测量之间的误差极小,只差几万分之一,折算下来接近-100dB了。

举个例子可能更容易说明我要说的。假设一中频是个1MHz正弦波。二本振也是个1MHz正弦波。两个向量完...

这个频率偏差是可以忽略的,只要偏差比中频带宽的二分之一小,影响就不大。当然,在一次校准及随后的测试中,偏差不能有太大变化,不然中频通带的形状(包括群延迟)会对测试结果产生影响。

另外,S11的测量极限其实取决于负载(SOLT校准时),最好的负载也不过三四十dB。你说的似乎是对的,低的噪底可能在测试小反射时,减少误差和抖动,只是我觉得在这种情形下也不用追求太高精度,回损-40和-41有区别吗。。。

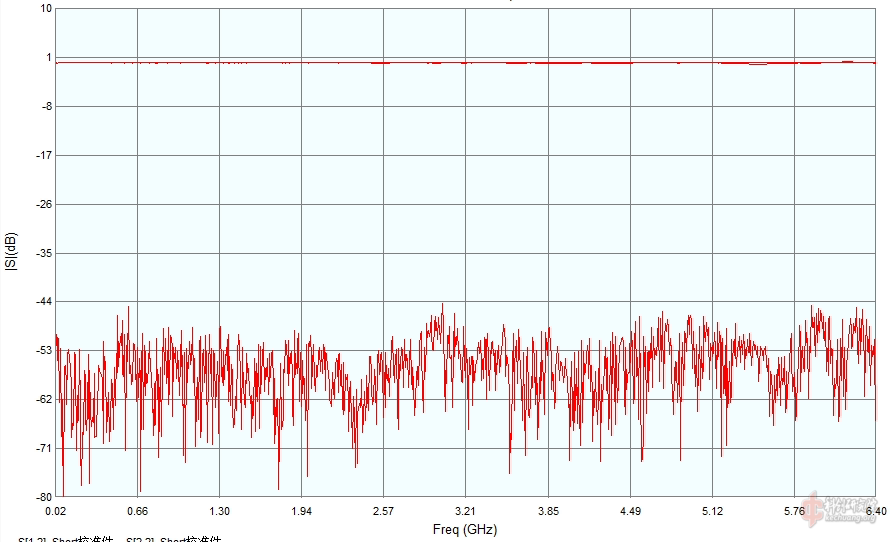

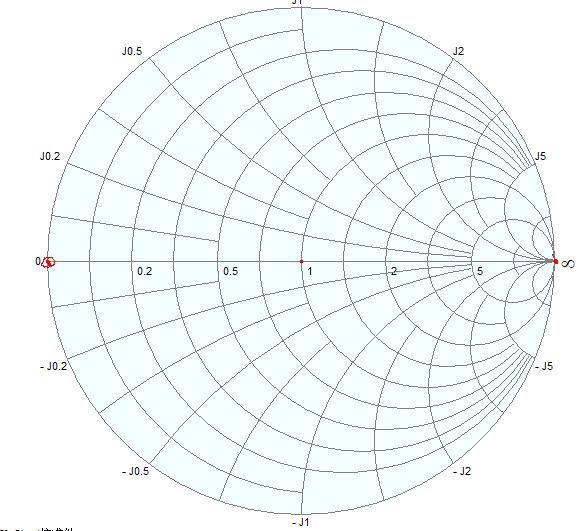

这是我当年鼓捣完之后,测三个校准件的结果。可以看出,load就在负六十附近晃悠。最高点都到负40多了。我当年就终止于此,不再鼓捣了。后来就搬家了。

这个频率偏差是可以忽略的,只要偏差比中频带宽的二分之一小,影响就不大。当然,在一次校准及随后的测试中...

就是不好说啊,如果CPU用里边的RC振荡器的话,可能频率偏差不小。所以这是我猜测原作者的设计为什么让CPU启动起来以后改选射频时钟做自己的时钟的原因。

我看了老的nanoVNA代码发现中频滤波是采用IIR+FIR带通方式进行滤波的(音频ADC芯片内部配置下寄存器即可),但是最新的代码却没有找到中频滤波器参数设置的地方,那就不知道它中频是怎么处理的了(最新的代码BW带宽用户可变了)。

算是内积。就是用FPGA运算出来的二本振SIN和COS两个三角函数信号,分别与refr,refl,t...

就是用FPGA运算出来的二本振SIN和COS两个三角函数信号,分别与refr,refl,through三个一中频信号做乘加,积分得到三个IQ,也就是你说的内积。

不就是数字下变频加积分求和吗?

就是用FPGA运算出来的二本振SIN和COS两个三角函数信号,分别与refr,refl,throug...

原理上一中频要过低通或带通,把ADC的Fs/2以上的频率,甚至把一中频的高次谐波尽量都过滤掉再过ADC。这样的话一中频是很纯净的正弦波。二本振(数字正余弦序列)就可以比较粗糙地生成了(不在乎二本振的高次谐波了),每周期几个样点即可。我当年是每周期8个样点。

当然最好的方式是一中频和二本振都做成良好的正弦波(高次谐频很小),这样两者做相关运算时不会把高次谐频的相关结果混入基频的相关结果。

原理上,如果一中频滤得非常纯净,那么二本振做成开关信号都可以。即二本振做成0101...或正负正负...序列都行。这样的二本振有大量高次谐波,但是因为一中频只有基波,高次谐波和基波的相关性为0,不会体现在内积结果中。

工程上当然是两者都滤一下更好。

200字以内,仅用于支线交流,主线讨论请采用回复功能。