TCD1209D是由TOSHIBA公司生产的一种高速、高灵敏度、低暗电流的双沟道、二相阵线阵CCD图像传感器,可用于传真、扫描和光学字符识别(OCR)等。该器件内含2088和高灵敏度PN结光电二极管构成的光敏元阵列,其中前32个和后8个用作暗电流检测而被遮蔽,中间2048个光电二极管是可曝光光敏单元,每个光敏单元尺寸为14μm×14μm×14μm,光敏阵列总长28.6mm,最佳工作频率1MHz,最大工作频率20MHz。

32148

%7B%22isLastPage%22%3Atrue%2C%22notes%22%3A%5B%5D%2C%22pid%22%3A%22t32148%22%2C%22tid%22%3A%2232148%22%2C%22mainForumsId%22%3A%5B%2237%22%5D%2C%22categoriesId%22%3A%5B%2250%22%5D%2C%22tcId%22%3A%5B%5D%7D

%7B%22isEditMode%22%3Afalse%7D

小线阵 TCD1209 CCD驱动入门

TCD1209D是由TOSHIBA公司生产的一种高速、高灵敏度、低暗电流的双沟道、二相阵线阵CCD图像传感器,可用于传真、扫描和光学字符识别(OCR)等。该器件内含2088和高灵敏度PN结光电二极管构成的光敏元阵列,其中前32个和后8个用作暗电流检测而被遮蔽,中间2048个光电二极管是可曝光光敏单元,每个光敏单元尺寸为14μm×14μm×14μm,光敏阵列总长28.6mm,最佳工作频率1MHz,最大工作频率20MHz[33]。TCD1209D的特征参数如下表所示,测试条件:环境温度25°C,驱动频率为1MHz,积分时间为10ms,负载电阻为100KΩ时在2856K标准白炽灯光源情况下的特征参数。

特征参数 | 参数符号 | 最小值 | 典型值 | 最大值 | 单位 |

| 驱动频率 | f | | 1 | 20 | MHz |

| 动态范围 | | 2000 | | | |

| 灵敏度 | R | 25 | 31 | 37 | V/(lx.s) |

| 饱和曝光量 | 0.04 | 0.66 | | lx.s | |

| 输出信号的直流电位 | 4.0 | 5.5 | 7.0 | V | |

| 噪声 | | 0.6 | | mV | |

| 饱和输出电压 | 1.5 | 2.0 | | V | |

| 暗信号电压 | | 1.0 | 2.5 | mV | |

| 暗电流电压不均匀性 | | 1.0 | 2.5 | mV | |

| 直流功率损耗 | | 160 | 400 | mW | |

| 总转移效率 | TTE | 92 | 98 | | % |

| 输出阻抗 | | 0.2 | 1 | KΩ | |

| 像敏单元的不均匀性 | PRNU | | 3 | 10 | % |

| PRNU(V) | | 4 | 10 | mV |

TCD1209D驱动脉冲时序结构如下图所示,分析此图知CCD的一个工作周期分为两个阶段:光积分阶段和电荷转移阶段。在光积分阶段,即当SH为低电平时,SH的低电平形成的浅势阱将存储栅势阱与Φ电极下的势阱相隔离,存储栅势阱积累光电二极管产生的光电荷;与此同时转移机构将上一帧转移到模拟移TCD1209D驱动脉冲时序结构如下图所示,分析此图知CCD的一个工作周期分为两个阶段:光积分阶段和电荷转移阶段。在光积分阶段,即当SH为低电平时,SH的低电平形成的浅势阱将存储栅势阱与Φ电极下的势阱相隔离,存储栅势阱

积累光电二极管产生的光电荷;与此同时转移机构将上一帧转移到模拟移位寄存器中的电荷输出并清空像元存储栅势阱中的无效电荷。当SH为高电平,Φ电极下的深势阱与MOS电容的深势阱相沟通,MOS电容的电荷信号包通过转移栅转移到模拟移位寄存器的Φ电极下的深势阱中,此时时钟脉冲停止工作,输出端没有有效信号输出,一个转移信号周期对应一帧光积分电荷的转移,为了确保每一帧信息的完全转移和可靠读出,CCD器件一般会在每行前后设置若干被遮蔽的无效像元,同时这些无效像元还用作暗电流检测。

上图和下表分别为东芝公司提供的TCD1209D芯片工作手册中的驱动时序脉冲时间要求,其中典型值是在RS脉冲频率为1MHz时的测量值,视频数据时延为负载电阻为100KΩ时的测量值。

[align=center][table]

特征

符号

最小值

典型值

最大值

单位

SH与Φ1脉冲计时t1,t5

200

500

—

ns

SH脉冲上升沿,下降沿时间t2,t4

0

50

—

ns

SH脉宽t3

1000

1500

—

ns

Φ2B脉冲上升沿,下降沿时间t6,t7

0

100

—

ns

RS脉冲上升沿,下降沿时间t8,t10

0

20

—

ns

RS脉宽t9

10

100

—

ns

视频数据时延t11

—

15

—

ns

CP脉冲上升沿,下降沿时间t12,t14

0

20

—

ns

CP脉宽t13

10

100

—

ns

CP与Φ2B脉冲计时t15

0

50

—

ns

CP与RS脉冲计时t16

0

100

—

ns

t1710

100

—

CP与SH脉冲计时t18

200

—

—

ns

[tr]RS与SH脉冲计时t19

200

—

[td=1,1,63][align=center][b]—[/sup][/align][/td]ns

[/tr][/table][/align]对于TCD1209D正常工作的时序要求,其中要强调的一点,即SH和Φ1、Φ2脉冲之间的关系。当SH为高电平时Φ1也必须同步为高电平,当SH为低电平时Φ1也要低下来。但是Φ1脉冲必须比SH脉冲提前上升、迟后下降,其延时至少200ns:Φ1脉冲先上升意味着模拟移位寄存器中接受电荷包的势阱先形成,有利于电荷转移;Φ1脉冲比SH脉冲后下降到低电平是使存储栅和模拟移位寄存器隔离,以免Φ1电极下的电荷倒回到原势阱中去。由于结构上的安排,OS端首先输出13个虚设单元信号,再输出19个暗信号,然后才连续输出S1到S2048的有效像素单元信号。在S2048信号输出后,又分别输出7个信号,再输出一个奇偶检测信号,以后是为调节积分时间而插入的若干个空驱动周期。

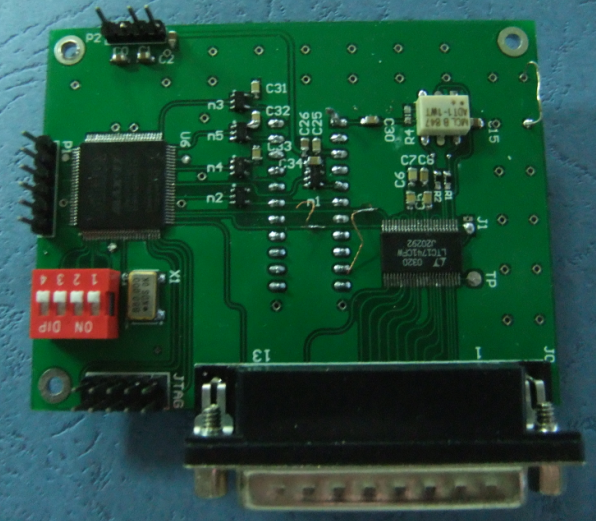

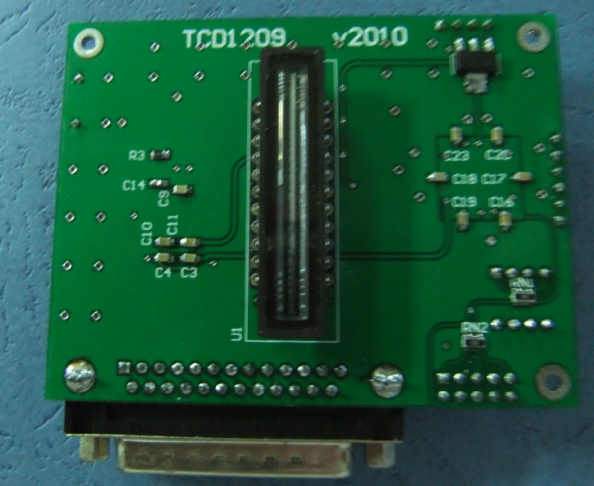

根据系统工作的最高频率要求,TCD1209D的最高工作频率为20MHz,所以本文选用80MHz晶振,进行4等分分频。整个设计包含6个功能模块,以下将按照模块逐一介绍其功能和设计思想:

(1)phi模块,为实现Φ1和Φ2的生成提供初始信号。此模块对晶振进行4分频,以clk时钟的上升沿作为有效信号,通过对clk的计数实现维持2个时钟周期的高电平,2个时钟周期的低电平,得到20MHz的工作频率。如果想得到1MHz的工作频率,可对clk计数,维持40个时钟周期的高电平,40个时钟周期的低电平,其他工作频率可同理实现。

(2)sh模块,用来产生SH信号。因Φ1与RS周期相同,以phi的上升沿作为响应信号,并对phi进行计数,因为1个周期至少包含2088个Φ1脉冲,并包含至少1个Φ1周期的高电平。此模块与phish模块结合,利用上一节提出的方法,即可对ADC输出延时造成的缺点进行修正。

(3)phish模块,这个模块的功能是对phi的“非”进行计数,维持2087个phi周期的低电平后,产生维持3个phi周期的高电平。这个模块与phi的“非”进行“或”运算以后,产生了最终的Φ1和Φ2。

(4)rscp模块,顾名思义,产生RS和CP的模块,对clk进行占空比为1:3的4分频,根据时序图,在Φ1的高电平期间,RS和CP相继产生高电平,可通过计数来产生,当SH为高电平的时候,满足RS、CP为低电平。

(5)sample模块,产生与phi信号有一个clk周期的相位差的信号,这样的信号可以利用上升沿对OS信号进行采样,经后面的sm_clk模块处理后,即可成为真正的AD9445采样时钟信号。关于采样时刻的选择,

(6)sm_clk模块,产生提供给AD9445的差分时钟信号,以RS的上升沿为有效信号,对RS进行计数,当超过32到2093时产生高电平作为sample输出的使能信号,同时对sample取“非”,即可输出两路差分时钟信号。

有一点需要注意:从CPLD芯片输出的信号是3.3V的LVCOMS信号,而TCD1209D使用的是5V驱动信号,故CPLD输出的信号不能直接加到CCD芯片上,为解决这一问题,采用外围电路提高驱动能力。本系统采用的是反相驱动器驱动原理产生CCD驱动时序,不但使信号能够满足CCD的需求,而且大大简化了电路设计,提高了可靠性,降低了功耗。同时由于反相驱动器对信号作了反相,因此在实际使用时在原理图顶层文件中CCD各时序信号输出也各接了一个非门,保证信号输出一致。

选定器件型号以后,在QuartusII下编译成功,设计占用逻辑单元占器件总逻辑单元的88%,管脚占总数的20%,可见器件的选型非常合适。因为MAXII CPLD供给TCD1209D的时钟经过一个反相器以增强驱动能力,所以仿真波形应该是与真正的驱动时序呈反相关系,下图为仿真波形。

选定器件型号以后,在QuartusII下编译成功,设计占用逻辑单元占器件总逻辑单元的88%,管脚占总数的20%,可见器件的选型非常合适。因为MAXII CPLD供给TCD1209D的时钟经过一个反相器以增强驱动能力,所以仿真波形应该是与真正的驱动时序呈反相关系,下图为仿真波形。

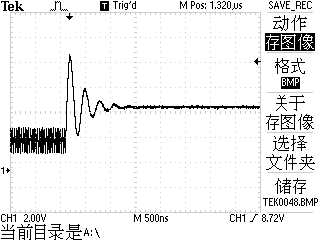

通过JTAG口将程序下载到MAXII CPLD器件中,用示波器观察其提供给CCD的驱动脉冲时序信号、提供给LTC1741的采样时钟,以及CCD的OS管脚输出信号,如图,由于TCD1209的典型工作频率是1Mz,我们先测试了工作频率为1MHz时的CCD驱动时序,可见其完全满足芯片正常工作的要求,并为LTC1741提供了差分采样时钟,且正向采样时钟的上升沿可以保证LTC1741采样到正确的数据。

提高驱动时钟频率到10MHz,此时CCD工作在10MHz。由于PCB分布参数的影响,信号质量明显变差,但仍可满足CCD工作的要求。由于此时CCD工作频率较高,相应的积分时间很短,普通的灯光下OS信号很弱,故在测试中使用小功率半导体激光器作为照明光源。

从示波器观测到的波形来看,矩形脉冲的边沿已经很不理想,造成这种情况的有可能是因为PCB设计时阻抗考虑不周。而且由于CCD可以看做是一个容性负载,高速工作下要获得好的边沿特性对驱动信号的驱动能力特别是灌电流能力和泄流电阻要求比较严格,本设计中采用的是非门进行驱动,驱动能力有限。建议以后可以尝试添加快速放电部分,并适当加强驱动能力。

按照CCD工作原理,在不同光照条件下,CCD的输出信号OS电平也应有所差别,在保证CCD不溢出情况下光强越强,CCD输出OS波形电压幅值越大。如下图所示分别为三种光强条件下的OS输出波形图。我们通过照度计(型号为ZDS-10)测量弱光时光照度为2.38(lx),中等光强时光照度为12.8(lx) ,强光时光照度为26.5(lx)。从示波器上观察到弱光时 Vpp=0.7V,中等光强时Vpp=1.26V,强光时Vpp=1.86V,从图中可以看出,随着光强的增大,CCD的输出信号OS的电压也增大。

另外在调试CCD信号采集板时,为防止意外损坏CCD芯片,应先用万用表测量CCD芯片插座各管脚的电压值,观察是否在正常范围内,再用示波器探头检测各插座中各个CCD所需时序脉冲波形、相位是否正确,最后关掉电源插上CCD芯片。

对1209的输出电压范围,以及用ad829运放进行二阶带通滤波时,正在研究中,非常感谢!

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

请问 RF Trans A 是什么型号,起什么作用,在别的资料中这个地方用的是运放的。这里好像是变压器?望详解!

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 4楼(bvv) 的帖子

ADT 1-1

不需要直流分量、不需要增益,用巴伦方便些

不需要直流分量、不需要增益,用巴伦方便些

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

谢谢LZ分享,很好的帖子。。。正为CCD发愁呢。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

你好,前辈,我有个问题想请教你,我在使用反相器升压时出现下面的情况

![1202_732f132150830375f87e6038aec82.bmp]()

,

这个图是水平驱动信号经反相后输出的图,频率28M,振荡的地方是向水平消隐期过度的时候,并且CCD输出有问题,噪声盖住信号,不知道你遇到过这样的问题没有,多谢了,期待回复。

,

这个图是水平驱动信号经反相后输出的图,频率28M,振荡的地方是向水平消隐期过度的时候,并且CCD输出有问题,噪声盖住信号,不知道你遇到过这样的问题没有,多谢了,期待回复。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

楼主最近不上来看看了吗?现再想用你的电路做CCD采集。但那个隔离变压器在哪能买到?

CCD出来的信号不用前级放大吗?

CCD出来的信号不用前级放大吗?

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 8楼(lostbooker) 的帖子

怎么下面看起来那么丑。。振铃估计是没匹配好,CCD是容性负载

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 11楼(plcpro) 的帖子

ADT 1-1 淘宝上很多,通信上很常用的。

或者直流耦合,直接运放转差分进AD

这个CCD的输出有2V左右,不需放大

或者直流耦合,直接运放转差分进AD

这个CCD的输出有2V左右,不需放大

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 4楼(bvv) 的帖子

CCD输出OS信号较弱、有增益需求时用运放,无增益需求是用巴伦更省事

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

正在研究tcd1209做毕业设计,谢谢楼主分享![s:274]

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

你好,有个关于线阵ccd的问题想请教一下!我的ccd tcd1209接上电源和驱动后,怎么都没有输出,只有十几毫伏的输出。我在不接驱动的情况下给电源端加12v的电压来测它的输出脚也没反应,连直流分量也没有!请问这是什么问题,我的ccd是否已经坏了!

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

爱死lz了

我也在研究ccd tcd1304

现在打算用几个单片机直接产生驱动信号 芯片刚到 查资料中

芯片有如此多的nc端 可不可以不接地?

我也在研究ccd tcd1304

现在打算用几个单片机直接产生驱动信号 芯片刚到 查资料中

芯片有如此多的nc端 可不可以不接地?

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 18楼(布布卡) 的帖子

不接地,为了减小焊盘占地面积把他们掰掉都行,我就是这么干的..

以下是我写的软件时序,用了一年没问题,用的是STM32F103C8T6,可以参考参考..

注意M之前已经配置成用TIM2产生4MHz的方波,进入函数时用GPIOB->CRH &= 0xfffff3ff;这个语句将M管脚切换到软件控制,退出时再切回4MHz方波

do..while那个循环的时序是用示波器一点一点调出来的,为了使M的波形尽量接近方波,所以把控制ADC读ADC都分成了若干个步骤

#define ICG PAout(1)

#define M PBout(10)

#define SH PAout(2)

#define M_H M=1

#define M_L M=0

//为了加快时钟M的速度,用GPIO的BSRR寄存器进行修改M的电平

//如果改了M的管脚,千万记得把这也改了!

#define M_H_FAST GPIOB->BSRR = 1<<10//M=1

#define M_L_FAST GPIOB->BSRR = 1<<(10+16)//M=0

#define ICG_L ICG=0

#define ICG_H ICG=1

#define SH_L SH=0

#define SH_H SH=1

void __inline delay(int n)

{

while(n--);

}

//-------------------------------------------------------------------

//从TCD1304中读取一帧

//注意第一个值是错误的,即pFrame[0]无效,pFrame[3694]缺失

//入口lExposeTime, *pFrame,是否开激光

//-------------------------------------------------------------------

void TCD1304GetFrame (int lExposeTime, short* pFrame, unsigned int u32NumOFPixel, int lIfLaser)

{

int u16Tmp;

if(lExposeTime<0)

lExposeTime = 0;

if(lIfLaser)//判断是否允许开激光

GPIOA->BSRR = 0x0100;//开激光

delay( 10 );//等待激光亮

ICG_H;//拉高ICG

M_H;//拉高M

SH_L;//拉低SH开始曝光

delay( lExposeTime );//延时一段时间

ICG_L;ICG_L;ICG_L;ICG_L;ICG_L;//关ICG,那么多次是为了延时

SH_H;//拉高SH,开始转移

delay( lExposeTime );//再延时一段曝光时间

SH_L;//拉低SH关曝光

GPIOA->BRR = 0x0100;//关激光 //当前激光亮灯时间 = 0.2498 * lExposeTime + 3.11 us

delay( T1 );

GPIOB->CRH &= 0xfffff3ff;//将M设置成通用推挽

ICG_H;//ICG拉高

do //用do..while循环,这样的话1000时会采1001次,但第一次的没用,所以正好1000个像素点

{

M_L_FAST;

*pFrame = u16Tmp;//将ADC数据存入帧内存

M_H_FAST;

u16Tmp = (u32)(&ADC1->CR2);//取得ADC控制寄存器的内存地址

M_L_FAST;

*(u32*)(u16Tmp) |= ((uint32_t)0x00500000);//启动转换

M_H_FAST;

u16Tmp = (u32)(&ADC1->DR);//取得AD转换结果地址

M_L_FAST;

u16Tmp = *(u32*)(u16Tmp);//取得AD转换结果

M_H_FAST;

pFrame++;//帧内存地址增1

__nop();

__nop();

M_L_FAST;

u32NumOFPixel--;//循环次数减1

__nop();

__nop();

M_H_FAST;

}

while(u32NumOFPixel);

SH_H;

GPIOB->CRH &= 0xfffff0ff;

GPIOB->CRH |= 0x00000b00;//设置恢复用推挽以输出4MHz波

}

以下是我写的软件时序,用了一年没问题,用的是STM32F103C8T6,可以参考参考..

注意M之前已经配置成用TIM2产生4MHz的方波,进入函数时用GPIOB->CRH &= 0xfffff3ff;这个语句将M管脚切换到软件控制,退出时再切回4MHz方波

do..while那个循环的时序是用示波器一点一点调出来的,为了使M的波形尽量接近方波,所以把控制ADC读ADC都分成了若干个步骤

#define ICG PAout(1)

#define M PBout(10)

#define SH PAout(2)

#define M_H M=1

#define M_L M=0

//为了加快时钟M的速度,用GPIO的BSRR寄存器进行修改M的电平

//如果改了M的管脚,千万记得把这也改了!

#define M_H_FAST GPIOB->BSRR = 1<<10//M=1

#define M_L_FAST GPIOB->BSRR = 1<<(10+16)//M=0

#define ICG_L ICG=0

#define ICG_H ICG=1

#define SH_L SH=0

#define SH_H SH=1

void __inline delay(int n)

{

while(n--);

}

//-------------------------------------------------------------------

//从TCD1304中读取一帧

//注意第一个值是错误的,即pFrame[0]无效,pFrame[3694]缺失

//入口lExposeTime, *pFrame,是否开激光

//-------------------------------------------------------------------

void TCD1304GetFrame (int lExposeTime, short* pFrame, unsigned int u32NumOFPixel, int lIfLaser)

{

int u16Tmp;

if(lExposeTime<0)

lExposeTime = 0;

if(lIfLaser)//判断是否允许开激光

GPIOA->BSRR = 0x0100;//开激光

delay( 10 );//等待激光亮

ICG_H;//拉高ICG

M_H;//拉高M

SH_L;//拉低SH开始曝光

delay( lExposeTime );//延时一段时间

ICG_L;ICG_L;ICG_L;ICG_L;ICG_L;//关ICG,那么多次是为了延时

SH_H;//拉高SH,开始转移

delay( lExposeTime );//再延时一段曝光时间

SH_L;//拉低SH关曝光

GPIOA->BRR = 0x0100;//关激光 //当前激光亮灯时间 = 0.2498 * lExposeTime + 3.11 us

delay( T1 );

GPIOB->CRH &= 0xfffff3ff;//将M设置成通用推挽

ICG_H;//ICG拉高

do //用do..while循环,这样的话1000时会采1001次,但第一次的没用,所以正好1000个像素点

{

M_L_FAST;

*pFrame = u16Tmp;//将ADC数据存入帧内存

M_H_FAST;

u16Tmp = (u32)(&ADC1->CR2);//取得ADC控制寄存器的内存地址

M_L_FAST;

*(u32*)(u16Tmp) |= ((uint32_t)0x00500000);//启动转换

M_H_FAST;

u16Tmp = (u32)(&ADC1->DR);//取得AD转换结果地址

M_L_FAST;

u16Tmp = *(u32*)(u16Tmp);//取得AD转换结果

M_H_FAST;

pFrame++;//帧内存地址增1

__nop();

__nop();

M_L_FAST;

u32NumOFPixel--;//循环次数减1

__nop();

__nop();

M_H_FAST;

}

while(u32NumOFPixel);

SH_H;

GPIOB->CRH &= 0xfffff0ff;

GPIOB->CRH |= 0x00000b00;//设置恢复用推挽以输出4MHz波

}

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

卧槽回顾一下代码发现

"GPIOB->CRH &= 0xfffff3ff;//将M设置成通用推挽"

这行位置貌似错了...会导致实际上之前进入函数的M管脚操作是无效的... 不过不管了至少这段代码是好使的.. 还有就是ADC要超频到18MHz,即72MHz主频时ADC四分频,不然速度不够.

上面那段代码有个缺陷, 至今没有找到为什么, 就是如果我改了程序别的地方, 跟这个函数无关, 编译, 下载运行, 可能会发现得到数据的灵敏度跟上次程序不一样了, 不过暗像素的位置是对的, 也就是说做一维的位置测量没问题, 但做亮度测量就不行了

实际上试过用STM32的定时器可以做到用两个定时器同步, 一个产生4MHz时钟驱动M一个产生1MHz时间触发ADC, DMA存ADC转换结果. 这招得出的图像质量很好因为M时钟是标准方波, 但应该是我写的时序有问题导致上一帧和下一帧得到的暗像素的位置会变化, 也就是说整帧会莫名其妙左右平移. 由于我做的是测量, 这样得到的帧需要先定位暗像素的位置之后才能进行下一步处理, 计算速度会慢一些, 所以最后还是用上面的软件控制ADC来采集

如果楼上上需要的话PM邮箱我我把整个工程发过去.. 由于做的玩意需要保密一段时间不宜公开所以就不上传了大家见谅...

"GPIOB->CRH &= 0xfffff3ff;//将M设置成通用推挽"

这行位置貌似错了...会导致实际上之前进入函数的M管脚操作是无效的... 不过不管了至少这段代码是好使的.. 还有就是ADC要超频到18MHz,即72MHz主频时ADC四分频,不然速度不够.

上面那段代码有个缺陷, 至今没有找到为什么, 就是如果我改了程序别的地方, 跟这个函数无关, 编译, 下载运行, 可能会发现得到数据的灵敏度跟上次程序不一样了, 不过暗像素的位置是对的, 也就是说做一维的位置测量没问题, 但做亮度测量就不行了

实际上试过用STM32的定时器可以做到用两个定时器同步, 一个产生4MHz时钟驱动M一个产生1MHz时间触发ADC, DMA存ADC转换结果. 这招得出的图像质量很好因为M时钟是标准方波, 但应该是我写的时序有问题导致上一帧和下一帧得到的暗像素的位置会变化, 也就是说整帧会莫名其妙左右平移. 由于我做的是测量, 这样得到的帧需要先定位暗像素的位置之后才能进行下一步处理, 计算速度会慢一些, 所以最后还是用上面的软件控制ADC来采集

如果楼上上需要的话PM邮箱我我把整个工程发过去.. 由于做的玩意需要保密一段时间不宜公开所以就不上传了大家见谅...

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 18楼(布布卡) 的帖子

不接地,为了减小焊盘占地面积把他们掰掉都行,我就是这么干的..

以下是我写的软件时序,用了一年没问题,用的是STM32F103C8T6,可以参考参考..

注意M之前已经配置成用TIM2产生4MHz的方波,进入函数时用GPIOB->CRH &= 0xfffff3ff;这个语句将M管脚切换到软件控制,退出时再切回4MHz方波

do..while那个循环的时序是用示波器一点一点调出来的,为了使M的波形尽量接近方波,所以把控制ADC读ADC都分成了若干个步骤

#define ICG PAout(1)

#define M PBout(10)

#define SH PAout(2)

#define M_H M=1

#define M_L M=0

//为了加快时钟M的速度,用GPIO的BSRR寄存器进行修改M的电平

//如果改了M的管脚,千万记得把这也改了!

#define M_H_FAST GPIOB->BSRR = 1<<10//M=1

#define M_L_FAST GPIOB->BSRR = 1<<(10+16)//M=0

#define ICG_L ICG=0

#define ICG_H ICG=1

#define SH_L SH=0

#define SH_H SH=1

void __inline delay(int n)

{

while(n--);

}

//-------------------------------------------------------------------

//从TCD1304中读取一帧

//注意第一个值是错误的,即pFrame[0]无效,pFrame[3694]缺失

//入口lExposeTime, *pFrame,是否开激光

//-------------------------------------------------------------------

void TCD1304GetFrame (int lExposeTime, short* pFrame, unsigned int u32NumOFPixel, int lIfLaser)

{

int u16Tmp;

if(lExposeTime<0)

lExposeTime = 0;

if(lIfLaser)//判断是否允许开激光

GPIOA->BSRR = 0x0100;//开激光

delay( 10 );//等待激光亮

ICG_H;//拉高ICG

M_H;//拉高M

SH_L;//拉低SH开始曝光

delay( lExposeTime );//延时一段时间

ICG_L;ICG_L;ICG_L;ICG_L;ICG_L;//关ICG,那么多次是为了延时

SH_H;//拉高SH,开始转移

delay( lExposeTime );//再延时一段曝光时间

SH_L;//拉低SH关曝光

GPIOA->BRR = 0x0100;//关激光 //当前激光亮灯时间 = 0.2498 * lExposeTime + 3.11 us

delay( T1 );

GPIOB->CRH &= 0xfffff3ff;//将M设置成通用推挽

ICG_H;//ICG拉高

do //用do..while循环,这样的话1000时会采1001次,但第一次的没用,所以正好1000个像素点

{

M_L_FAST;

*pFrame = u16Tmp;//将ADC数据存入帧内存

M_H_FAST;

u16Tmp = (u32)(&ADC1->CR2);//取得ADC控制寄存器的内存地址

M_L_FAST;

*(u32*)(u16Tmp) |= ((uint32_t)0x00500000);//启动转换

M_H_FAST;

u16Tmp = (u32)(&ADC1->DR);//取得AD转换结果地址

M_L_FAST;

u16Tmp = *(u32*)(u16Tmp);//取得AD转换结果

M_H_FAST;

pFrame++;//帧内存地址增1

__nop();

__nop();

M_L_FAST;

u32NumOFPixel--;//循环次数减1

__nop();

__nop();

M_H_FAST;

}

while(u32NumOFPixel);

SH_H;

GPIOB->CRH &= 0xfffff0ff;

GPIOB->CRH |= 0x00000b00;//设置恢复用推挽以输出4MHz波

}

以下是我写的软件时序,用了一年没问题,用的是STM32F103C8T6,可以参考参考..

注意M之前已经配置成用TIM2产生4MHz的方波,进入函数时用GPIOB->CRH &= 0xfffff3ff;这个语句将M管脚切换到软件控制,退出时再切回4MHz方波

do..while那个循环的时序是用示波器一点一点调出来的,为了使M的波形尽量接近方波,所以把控制ADC读ADC都分成了若干个步骤

#define ICG PAout(1)

#define M PBout(10)

#define SH PAout(2)

#define M_H M=1

#define M_L M=0

//为了加快时钟M的速度,用GPIO的BSRR寄存器进行修改M的电平

//如果改了M的管脚,千万记得把这也改了!

#define M_H_FAST GPIOB->BSRR = 1<<10//M=1

#define M_L_FAST GPIOB->BSRR = 1<<(10+16)//M=0

#define ICG_L ICG=0

#define ICG_H ICG=1

#define SH_L SH=0

#define SH_H SH=1

void __inline delay(int n)

{

while(n--);

}

//-------------------------------------------------------------------

//从TCD1304中读取一帧

//注意第一个值是错误的,即pFrame[0]无效,pFrame[3694]缺失

//入口lExposeTime, *pFrame,是否开激光

//-------------------------------------------------------------------

void TCD1304GetFrame (int lExposeTime, short* pFrame, unsigned int u32NumOFPixel, int lIfLaser)

{

int u16Tmp;

if(lExposeTime<0)

lExposeTime = 0;

if(lIfLaser)//判断是否允许开激光

GPIOA->BSRR = 0x0100;//开激光

delay( 10 );//等待激光亮

ICG_H;//拉高ICG

M_H;//拉高M

SH_L;//拉低SH开始曝光

delay( lExposeTime );//延时一段时间

ICG_L;ICG_L;ICG_L;ICG_L;ICG_L;//关ICG,那么多次是为了延时

SH_H;//拉高SH,开始转移

delay( lExposeTime );//再延时一段曝光时间

SH_L;//拉低SH关曝光

GPIOA->BRR = 0x0100;//关激光 //当前激光亮灯时间 = 0.2498 * lExposeTime + 3.11 us

delay( T1 );

GPIOB->CRH &= 0xfffff3ff;//将M设置成通用推挽

ICG_H;//ICG拉高

do //用do..while循环,这样的话1000时会采1001次,但第一次的没用,所以正好1000个像素点

{

M_L_FAST;

*pFrame = u16Tmp;//将ADC数据存入帧内存

M_H_FAST;

u16Tmp = (u32)(&ADC1->CR2);//取得ADC控制寄存器的内存地址

M_L_FAST;

*(u32*)(u16Tmp) |= ((uint32_t)0x00500000);//启动转换

M_H_FAST;

u16Tmp = (u32)(&ADC1->DR);//取得AD转换结果地址

M_L_FAST;

u16Tmp = *(u32*)(u16Tmp);//取得AD转换结果

M_H_FAST;

pFrame++;//帧内存地址增1

__nop();

__nop();

M_L_FAST;

u32NumOFPixel--;//循环次数减1

__nop();

__nop();

M_H_FAST;

}

while(u32NumOFPixel);

SH_H;

GPIOB->CRH &= 0xfffff0ff;

GPIOB->CRH |= 0x00000b00;//设置恢复用推挽以输出4MHz波

}

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 20楼(10班陈大葱22号) 的帖子

你在做激光雷达? 代码收下慢慢研究 因为目前我只想得到一个亮斑在ccd上的较准确位置 所以确定了采用输出信号二值化(复杂的以后再完善) +数字电路驱动 (2M晶振+反相器产生时钟M 之后进入4017进行分频 提供SH 之后单片机控制ICG和是否让SH使能 然后计时到二值化的信号电平翻转。。 )

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 22楼(布布卡) 的帖子

没在做激光雷达,做的是双目测目标角度算目标坐标的, 用在今年ABU robocon比赛上A机器人定位bud和跟M机器人对接, 绝对精度+/-0.01deg, 重复精度0.005deg

泪奔啊 机器人可靠性捉鸡 失误两次 比赛泥马连小组赛都没出线

oled上右上角是算出的坐标, 结果用CAN发出来, 处理器用两片STM32c8t6, 线阵用的是TCD1304, 取第100到1200像素因为20块钱镜头只能成像那么点= =, 整个玩意速度330Hz, 动态范围30000, 算法是32倍像素细分, 总共整了四个多月 主要是处理光路上材料受热线膨胀时掉精度的问题, 还有镜头成像的变形 最后是上精密分度台挨度标定然后高次拟合的...

激光雷达推荐用摄像头做,这样就不用旋转了,速度还快可以跑到30帧。不过处理器要求也高了,而且要测大视野的话要小焦距的镜头,测距精度低一些

点击此处查看视频

泪奔啊 机器人可靠性捉鸡 失误两次 比赛泥马连小组赛都没出线

oled上右上角是算出的坐标, 结果用CAN发出来, 处理器用两片STM32c8t6, 线阵用的是TCD1304, 取第100到1200像素因为20块钱镜头只能成像那么点= =, 整个玩意速度330Hz, 动态范围30000, 算法是32倍像素细分, 总共整了四个多月 主要是处理光路上材料受热线膨胀时掉精度的问题, 还有镜头成像的变形 最后是上精密分度台挨度标定然后高次拟合的...

激光雷达推荐用摄像头做,这样就不用旋转了,速度还快可以跑到30帧。不过处理器要求也高了,而且要测大视野的话要小焦距的镜头,测距精度低一些

点击此处查看视频

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 23楼(10班陈大葱22号) 的帖子

我做的没那么复杂 现在还没个底 到底能做出什么 主要是想玩玩 代替超声波测距 做个简易光谱仪

没几天就开学了就没空捣鼓了

没几天就开学了就没空捣鼓了

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

跟你一比,我都发觉我大学白过了。。。。[s:10]

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

I downloaded the program and I 've run .but the program did not catch.Why PH1 signal 11 units.You should try and 2048 needs.

[](XXXXXXXXXXXXXXXXXXXXX/JpPgRq)

please answer..

[](XXXXXXXXXXXXXXXXXXXXX/JpPgRq)

please answer..

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

求TCD1209D驱动程序

你好,楼主,我现在正在做毕业设计,但是遇到的比较大的问题就是这个TCD1209D的驱动问题,这个东西由于手里没有资料,所以好长时间都不能继续下去了,希望得到楼主的帮助。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

下载的压缩包里的文件用什么软件打开?

你好,楼主,我想问一下你上传的压缩包的文件用什么软件打开

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

请教您这款设计实际帧率能达到多少,理论上是10K的帧率对不,实际能达到多少请问有没有测试过,提供参考一下

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。