说了优点,谈谈这个拓扑在工程实施中的一些问题,

根据思路,我在Ltspice中搭建了一个仿真环境,由于Ltspice 没找到SCR的basic model

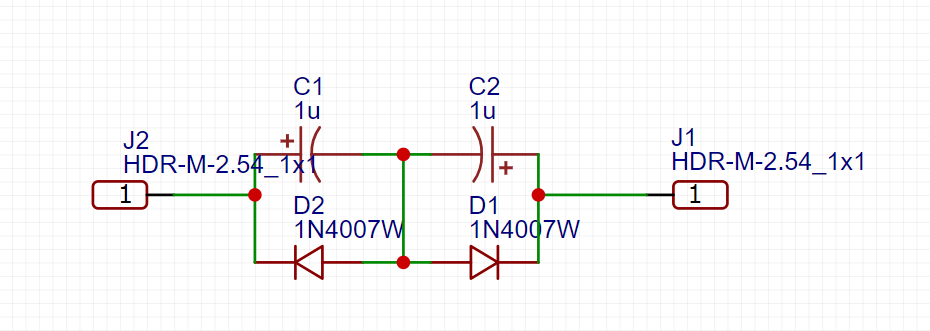

为了简单,根据.model SW的单向导通特性描述,配合二极管.model D可以构架出一个允许单向导通的SCR元件

SW1-4模拟Q1-Q4,SWa-d模拟Qa-Qd各级选通SCR开关

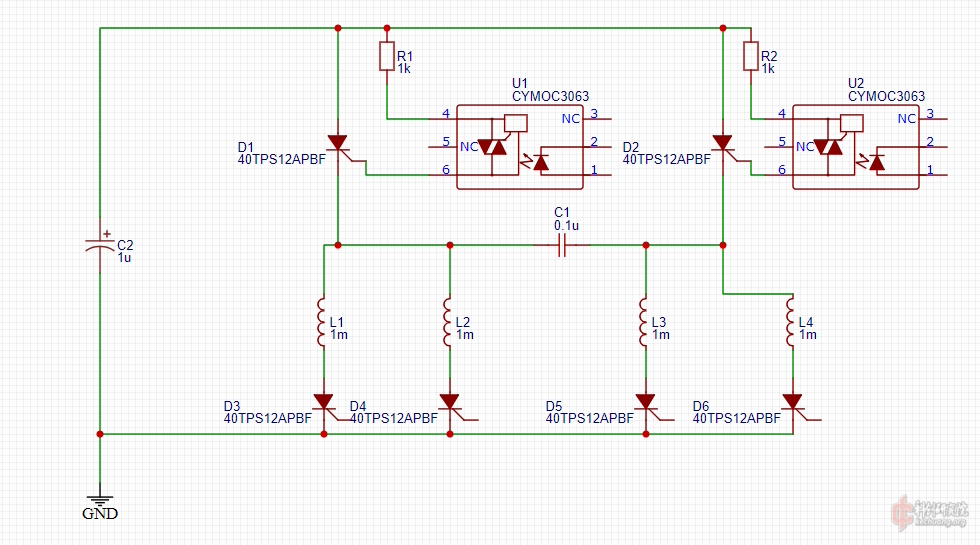

V1phase和V2phase分别通过behave voltage source来驱动S1-S4,提供全桥驱动信号(可控硅可只用脉冲上升沿)

现实中可对应为驱动全桥的两路半桥驱动PWM信号,

可以看到,在V1、2的有序驱动中,绿色电流部分 I(C1)被自身特性强制电流过0后关断,

留出了间隔,等待下一级信号的触发,可以看到当电流过零后,

由于线圈L1的续流作用,C1继续流过左到右的电流,让C的电压达到第一次回收电压平台700V左右。

此时下一级L2 SWb导通,相反的完成了一次以上过程,之后的两级是以上过程的重复。

可以看到,紫色电压在不断的放电中,不断得到续流能量的补充,越来越高,

电解电容仅仅450V的初始电压,在没有任何额外升压的情况下,

仅仅靠续流回收就实现了薄膜磁阻1.5KV储能,1KA的放电,在最后没有信号驱动后,C1维持在了1.5KV的电压。

-

可以通过仿真看到,该电路可以与定性分析中一样,实现仅仅以普通电解电容的电压和储能。

在1-2次放电内,实现在内达到薄膜磁阻的放电能力和续流回收特性,

把普通薄膜电容磁阻需要的N级电容,减少到了仅1个,通过交替利用,实现了高效体积利用。

同样可以发现,SCR的补充能量可以在电流过零点实现ZCS,损耗非常小

-

仅仅多出4个SCR和隔离驱动,和一个薄膜电容,即可实现N级薄膜磁阻能实现的效果。

但问题是,C1电容电压会不断振升,可能会超过C1的承载能力或耐压,不稳定的VC1也会导致难以仿真线圈参数

进一步的根据以上分析做仿真改进:

为了避免C1电容像荡秋千一样,被续流和补充能量不断的充到损坏,可以减小Csum的容量

由于每一级LC关断时间点的恒定,可以确定电压越低补充能量速度越慢,放电中递减的VCsum可以刚好匹配能量损耗

当Csum的容量刚好匹配到一个最佳值,可以让C1每次回收后的电压实现恒定。

通过人脑仿真 ,设置Csum(图中C2)=680uF,可以发现此时,紫色电压在四次开关回收中,可以近似恒定

,设置Csum(图中C2)=680uF,可以发现此时,紫色电压在四次开关回收中,可以近似恒定

而且由于电压恒定,绿色线圈电流,也近似恒定,

如果级数增加,可以根据能量消耗,计算出一个平均耗损能量,逐级加大电容量来实现对能量的逐级补偿,

让整个加速段,得到相同的C1电压,来让逐级加速性能维持恒定。

-

这样就实现了对这个拓扑结构的定性和定量分析。

200字以内,仅用于支线交流,主线讨论请采用回复功能。