很有用的参考资料。

十几年前刚画PCB时,小心翼翼的套用各种规则……慢慢一条条的抛弃规则……几年前画2.4G、5.8G、DDR2之类的板已经随心所欲了。——看来还是有依据的,呵呵

十几年前刚画PCB时,小心翼翼的套用各种规则……慢慢一条条的抛弃规则……几年前画2.4G、5.8G、DDR2之类的板已经随心所欲了。——看来还是有依据的,呵呵

[修改于 7年8个月前 - 2017/04/14 20:19:32]

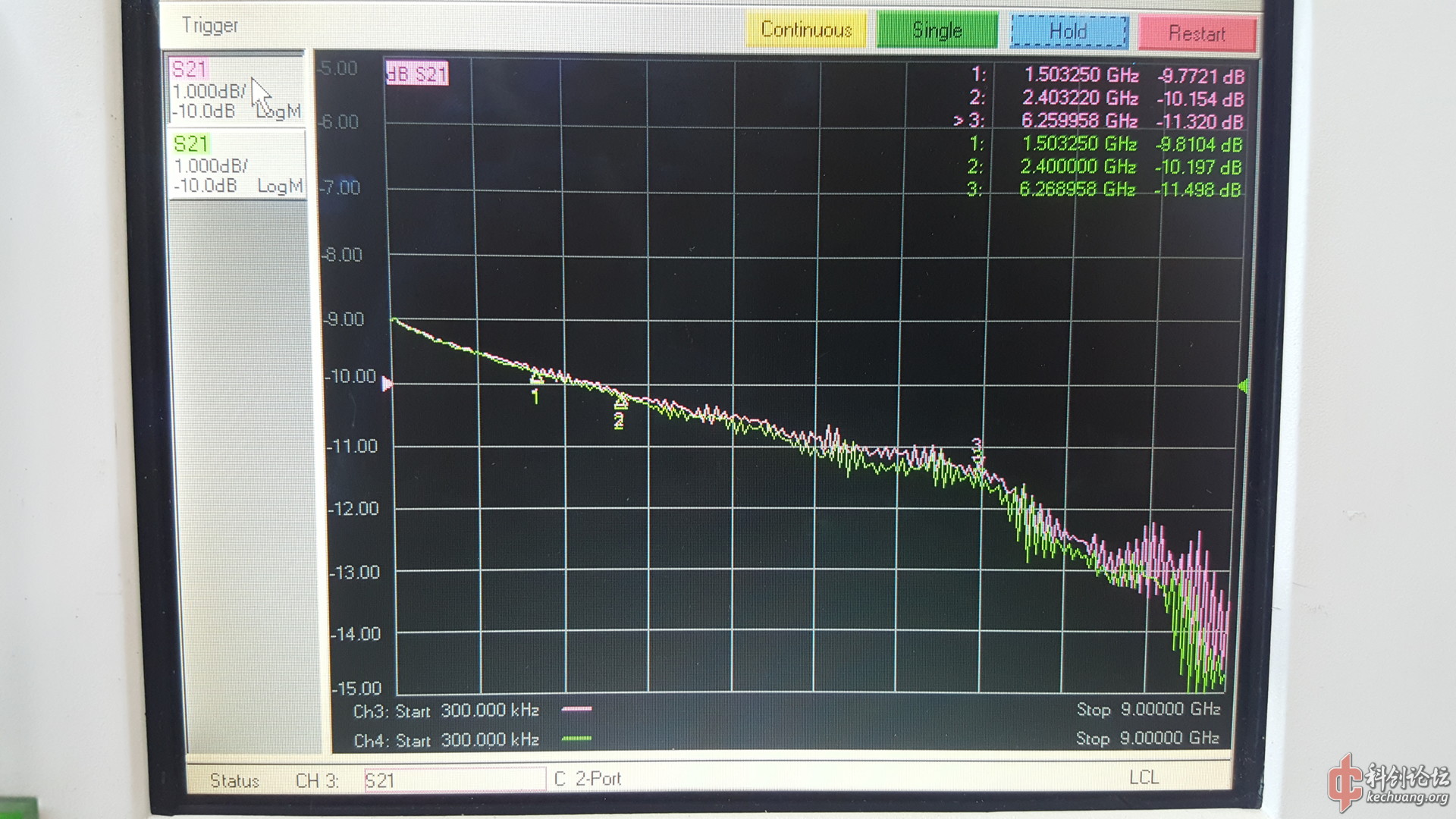

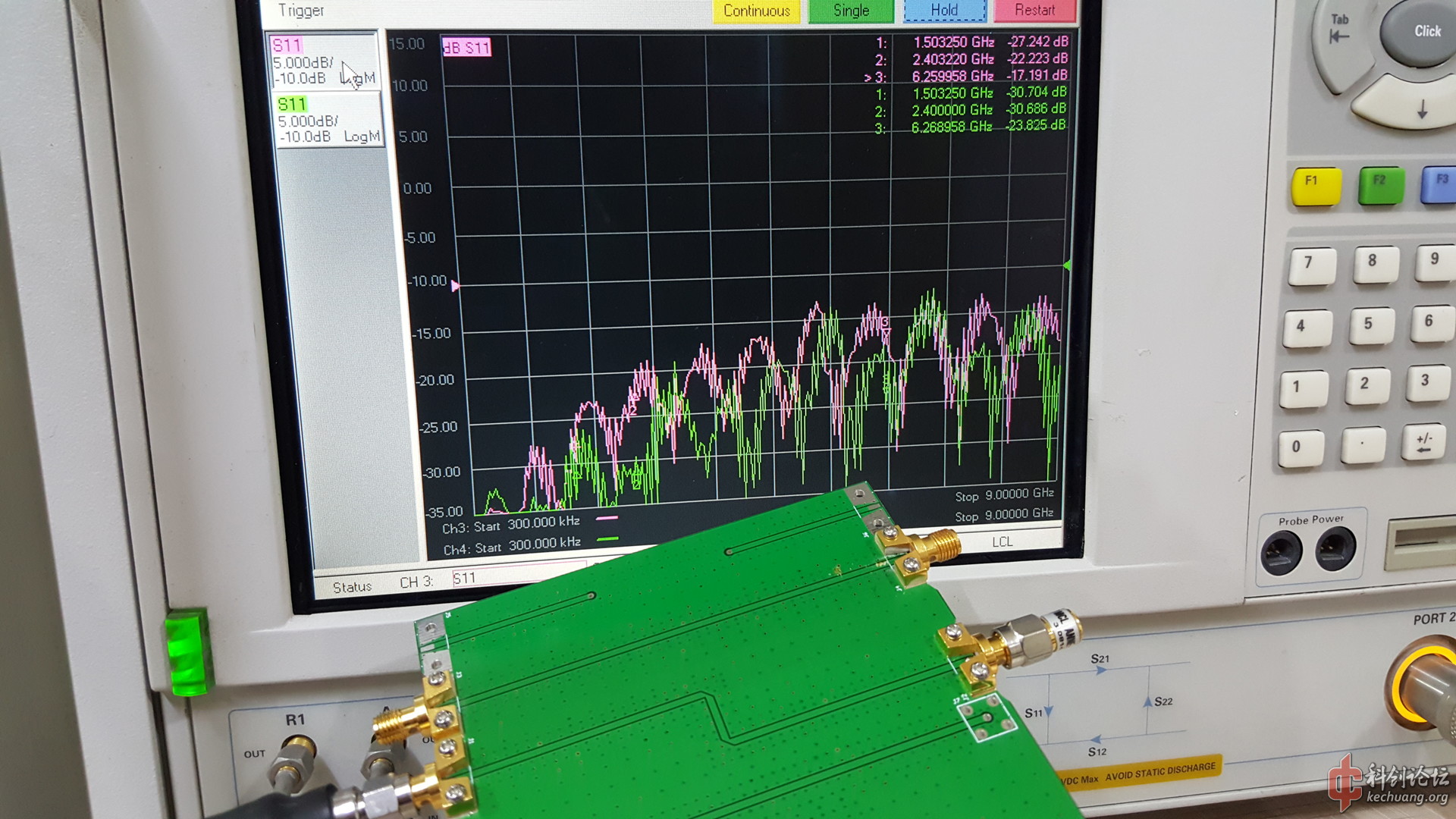

引用 量子隧道:其他人校准后2端口串了衰减器,我偷懒没取下来。直接测没这些波动。

不错的实验。

话说不知那些细密的起伏是从哪来的。按理说这种频域的细密起伏预示着在电距离相隔比较远的点之间有不匹配导致的信号长距离来回反射。是电缆的原因还是衰减器的原因?

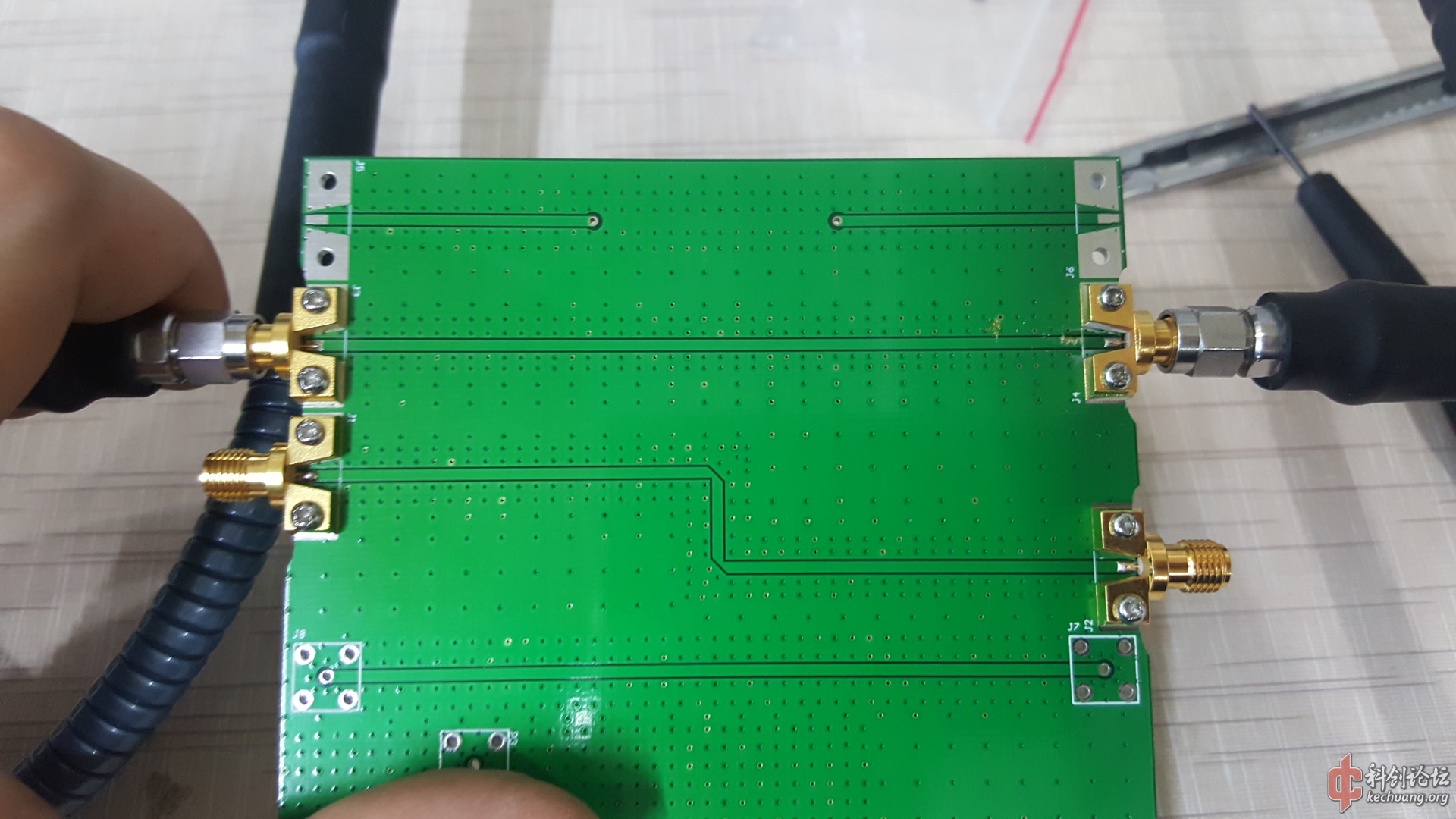

引用 wzh19940105:帖子里提到了做的是共面波导,除非减小板厚、更换介质,没办法拉开距离。

可以把微带线和覆铜的距离拉大一点 衰减会小一些

我用ro4350b做的板子 覆铜间距从10mil拉到30mil 衰减小了很多

引用 wzh19940105:加大铺铜间距的同时需加粗芯线,于是会减少损耗。坏处是多占面积,降低截止频率;由于线比焊盘大太多,也可能带来新的问题。

可以把微带线和覆铜的距离拉大一点 衰减会小一些

我用ro4350b做的板子 覆铜间距从10mil拉到30mil 衰减小了很多

引用 奉旨泡面:要知其所以然需要推公式。仿真也能达到知其然的结果。截角弯到底截多少性能最优?可以仿真确定。类似的各种小问题,我们做了很多仿真来确定对应的最优方法,设计的时候就很方便了。

好文章 一直用圆角 弧线转弯,知其然不知其所以然

引用 ddomax:我的理解是如果把共面波导的D1参数调到无穷大 那么就变成了微带线?

帖子里提到了做的是共面波导,除非减小板厚、更换介质,没办法拉开距离。

-----

补:当然还可以增加微带线宽度。不过双面板厚度较大,拉开距离恐怕微带线会太粗。

0.8mm板厚 FR4 35um铜厚

1……

引用 wzh19940105:

我的理解是如果把共面波导的D1参数调到无穷大 那么就变成了微带线?

引用 ddomax:非常感谢

是的。当间隙增大时,CPWG(共面波导 地平面)结构的特性就靠近Microstrip。

可以看到当D1=10000mils时,同阻抗下两者的线宽已经非常接近。

CPWG:

![3.jpg]()

M

引用 ddomax:加宽线宽来拉开距离应该有效,但是效果有限。共面波导损耗大的原因是趋肤效应和邻近效应。由于线的侧边紧靠地平面,电流过于集中在线的侧边流动,导致等效趋肤电阻加大,欧姆性损耗(铜损)加大。

帖子里提到了做的是共面波导,除非减小板厚、更换介质,没办法拉开距离。

-----

补:当然还可以增加微带线宽度。不过双面板厚度较大,拉开距离恐怕微带线会太粗。

0.8mm板厚 FR4 35um铜厚

1……

引用 虎哥:虎哥,冒味地问一句,您的手持矢网的定向电桥,是用的电阻桥(惠斯通电桥)还是微带线耦合器?

其他人校准后2端口串了衰减器,我偷懒没取下来。直接测没这些波动。

引用 量子隧道:现在电阻桥是主流,只是有多种不同形式的电阻桥,等臂的和不等臂的。前者我们用到7GHz,后者可以用到18GHz。

虎哥,冒味地问一句,您的手持矢网的定向电桥,是用的电阻桥(惠斯通电桥)还是微带线耦合器?

我最近在研究矢网的DIY。目前发现高频(4-6GHz)特性不太好,由于缺乏分析仪器,不知道是不是因为我采用了电……

引用 虎哥:多谢!电阻桥可以跑到18GHz,这确实有点出乎我的意料了。不过想想也应该可以。某宝上有卖号称能工作到20GHz的同轴电阻的,用来制作电阻桥应该很好。

现在电阻桥是主流,只是有多种不同形式的电阻桥,等臂的和不等臂的。前者我们用到7GHz,后者可以用到18GHz。

引用 量子隧道:你的意思是有20dB的定向性?这个已经可以了。

两臂的不平衡度已经达到了VL-VR=Vu/10的量级

引用 虎哥:是的,可以认为VL-VR=Vu/10,意味着当我认为电桥应该是平衡时,其实两臂已经有误差了,误差信号是入射到DUT的信号的10分之一,20log10(10)=20dB。

你的意思是有20dB的定向性?这个已经可以了。

引用 量子隧道:通俗而言,误差是因为空间尺寸导致的相位差不能忽略导致的,改善布局可减弱影响。贴片电阻的寄生电感大,少一个电容使两臂不完全对称,端口连接器有反射,都造成定向性下降。901大量使用定制器件,也不能良好消除的。对于vna,20dB很够了,校准完就会有60。你的VNA用在什么地方,需要多高的定向性?

是的,可以认为VL-VR=Vu/10,意味着当我认为电桥应该是平衡时,其实两臂已经有误差了,误差信号是入射到DUT的信号的10分之一,20log10(10)=20dB。

引用 虎哥:我的VNA是我自己业余鼓捣的,目前还未考虑商用。制作灵感来自于偶然网上翻到了这篇文章:

通俗而言,误差是因为空间尺寸导致的相位差不能忽略导致的,改善布局可减弱影响。贴片电阻的寄生电感大,少一个电容使两臂不完全对称,端口连接器有反射,都造成定向性下降。901大量使用定制器件,也不能良好消除……

引用 量子隧道:这篇文章用的是不等臂的电桥,根据他的选值,耦合度15dB水平,有潜力工作到很高频率(但难以下到低频)。建议就照他的办法做。当然,他的电路上有一些影响性能的坑,做商用产品需要改进。

我的VNA是我自己业余鼓捣的,目前还未考虑商用。制作灵感来自于偶然网上翻到了这篇文章:

引用 虎哥:不是。他这个单接收机方案,有个问题存在:在PLL刚刚完成锁定的前几个毫秒,其实信号还是有较大的频飘和抖动的(即使锁定后很久也存在)。那么通过用单接收机先后选择不同的源,我觉得很难保证先测量的信号和后测量的信号的相关性。

这篇文章用的是不等臂的电桥,根据他的选值,耦合度15dB水平,有潜力工作到很高频率(但难以下到低频)。建议就照他的办法做。当然,他的电路上有一些影响性能的坑,做商用产品需要改进。

你也是像他一样用一个……

引用 虎哥:他用的是传输线耦合器做的电桥,虽然原理上可以工作到很高频率,但是具体能到多高频率取决于设计(平行耦合长度)。

这篇文章用的是不等臂的电桥,根据他的选值,耦合度15dB水平,有潜力工作到很高频率(但难以下到低频)。建议就照他的办法做。当然,他的电路上有一些影响性能的坑,做商用产品需要改进。

你也是像他一样用一个……

引用 量子隧道:可能你没仔细看,他这个桥的构型能到多低主要靠磁环,图片中的长度到10M左右问题不大。而且不是传输线耦合,典型的不等臂电桥,设计靠经典电路理论。当然这个有窍门,没照他的做也是对的,现在想来,如果照他的做估计会坑,除非你有丰富的同轴巴伦制作经验,不然那些磁环的选择就是头疼事,当年我们把磁性材料厂折腾得够呛,不过结果是一个桥就能搞定10M-18G。遗憾的是后来要求必须覆盖到9k,所以这种桥没在产品中使用,我们就死磕电阻等臂桥解决了。

他用的是传输线耦合器做的电桥,虽然原理上可以工作到很高频率,但是具体能到多高频率取决于设计(平行耦合长度)。

耦合长度最佳值是1/4波长。频率上限越高,耦合长度越短。而耦合长度越短,低频耦合度越差。

引用 虎哥:

可能你没仔细看,他这个桥的构型能到多低主要靠磁环,图片中的长度到10M左右问题不大。而且不是传输线耦合,典型的不等臂电桥,设计靠经典电路理论。当然这个有窍门,没照他的做也是对的,现在想来,如果照他的做……

引用 虎哥:再看他的PCB的这两个部分,应该就是耦合器

可能你没仔细看,他这个桥的构型能到多低主要靠磁环,图片中的长度到10M左右问题不大。而且不是传输线耦合,典型的不等臂电桥,设计靠经典电路理论。当然这个有窍门,没照他的做也是对的,现在想来,如果照他的做……

引用 量子隧道:单节的平行耦合线定向耦合器原理上就是窄带器件。相同PCB面积的情况下,电阻性器件一般有更大的工作带宽。面积足够就可以考虑多节的微带耦合器。如果需要工作到直流,也只有电阻性器件可选。

他用的是传输线耦合器做的电桥,虽然原理上可以工作到很高频率,但是具体能到多高频率取决于设计(平行耦合长度)。

耦合长度最佳值是1/4波长。频率上限越高,耦合长度越短。而耦合长度越短,低频耦合度越差。

引用 ddomax:你说得对,电介质的均匀一致性是定向性的前提。电介质在横截面上各个点的介电常数一致,奇模波速和偶模波速相等,定向性就会好。

单节的平行耦合线定向耦合器原理上就是窄带器件。相同PCB面积的情况下,电阻性器件一般有更大的工作带宽。面积足够就可以考虑多节的微带耦合器。如果需要工作到直流,也只有电阻性器件可选。

提高奇模相速度,可……

引用 量子隧道:现在知道了,我看的是这一篇,同一个人的最新版作品:XXXXXXXXXXXXXXXXXXX/XXXXXXXXXXXXXXXXXXXXXXXXml

你看他的

“Design

Directional coupler”

那一节,文字和图片都是描述微带线耦合器的。

这是从里边摘出来的文字“Simulated directivity is 20 dB

引用 虎哥:哦,这位作者也转向电阻桥了。看来我当初的担忧是有道理的:)

现在知道了,我看的是这一篇,同一个人的最新版作品:XXXXXXXXXXXXXXXXXXX/XXXXXXXXXXXXXXXXXXXXXXXXml

这个是主流方案(单通道接收机除外)……

引用 量子隧道:明白了。你用的零中频或者低中频方案吗,一般对于s11这种小动态测试,pll噪声的影响不应该成为问题。

哦,这位作者也转向电阻桥了。看来我当初的担忧是有道理的:)

我还是较看重低频的测量精度的。我当时仿真了传输线耦合器,发现低频信号损失30dB。所以没用。

昨晚高频的问题原因找到了。是因为我在驱动PLL……

引用 虎哥:其实我上一个回复没说全。PLL选择不同的bank,输出功率电平会不一样。而我的PLL输出驱动一个射频功放,驱动功率较大,射频功放快饱和了,输出已经不线性了。此时系统功率电平改变,会影响S11测试结果。这导致了高频测试噪音。

明白了。你用的零中频或者低中频方案吗,一般对于s11这种小动态测试,pll噪声的影响不应该成为问题。

引用 量子隧道:这个方法还是比较科学的。我们是二次变频方案,没发现有问题。一个周期采几个点,只要符合采样定理就不是问题,理论上影响不大的,实际影响也不大。毕竟不是一个周期就出结果,随机抖动的影响有限。关于S11本底噪音,这个概念不太清晰,我没理解你的意思。如果论接收机,就是接收机底噪或者动态范围。如果论S11,它的测量范围一方面取决于电桥的定向性,另一方面取决于接收机的噪音(幅度,相位),因为接收机噪音大会导致校准后无法良好消除泄漏误差。通常20dB的桥定向性,经校准可获得-80dB或者更高的底噪(不考虑信号源和接收机性能的中长期漂移的情况下)。所以不清楚你说的到底是接收机噪底,还是校准后的相对定向性。

其实我上一个回复没说全。PLL选择不同的bank,输出功率电平会不一样。而我的PLL输出驱动一个射频功放,驱动功率较大,射频功放快饱和了,输出已经不线性了。此时系统功率电平改变,会影响S11测试结果。……

引用 虎哥:我是做完SOL三项校准后,测试50欧姆电阻(其实就是SOL里边的L)的反射S11,低频-60-70db;高频-50多dB。这应该算是底噪测试?还是定向性测试?

这个方法还是比较科学的。我们是二次变频方案,没发现有问题。一个周期采几个点,只要符合采样定理就不是问题,理论上影响不大的,实际影响也不大。毕竟不是一个周期就出结果,随机抖动的影响有限。关于S11本底噪……

引用 量子隧道:我也不知道“标准的”说法,只要让人明白意义,不与接收机本身的噪底混淆,说是定向性或者S11底噪应该都没问题。

我是做完OLT三项校准后,测试50欧姆电阻(其实就是OLT里边的T)的反射S11,低频-60-70db;高频-50多dB。这应该算是底噪测试?还是定向性测试?

引用 量子隧道:关于电桥,除了频率范围还有诸多指标,算不上太领先,10M-20G是十多年前的国外主流了(参考安捷伦5230)。倍频程似乎不是上限除以下限。。。

1,2收的意思就是让1端口发,测试1端口发射功率,1端口反射功率,2端口接收功率。我的DIY VNA是单向的,只有1端口能发射。

引用 虎哥:见笑了,应该说是1000倍的频率覆盖范围。

关于电桥,除了频率范围还有诸多指标,算不上太领先,10M-20G是十多年前的国外主流了(参考安捷伦5230)。倍频程似乎不是上限除以下限。。。

您的VNA如果需要做12参数校准,由于直通件可以认为是对……

引用 量子隧道:这个图不太对,如果是这个图,那就只能因为R4所占比例小,哈哈哈哈。

关于这个电桥,有一点很蹊跷:

![xbridge2.png.pagespeed.ic.JYjnr5IewJ.png]()

按理说,电桥的输出(反射信号的提取)应该在R3的两端,不知为啥在这里变成了在R3的左端。

引用 虎哥:假设电桥平衡,Z=50ohm。那么R2/R5刚好等于Z/R4。(Z按照比例1传递到变压器原边,作为一臂)。

这个图不太对,如果是这个图,那就只能因为R4所占比例小,哈哈哈哈。

引用 量子隧道:出于好奇,昨天我还找群里的朋友扒下来看了一下。其实天底下少有新鲜事,这个构型在我看到的资料中都已经出来快四十年了,2015年还能在会议上发这种文章,这会议果然是来者不拒(也许是MICRAN公司对此有历史贡献)。不过商用已经是上世纪80年代末的事情,从那以后该结构基本就统一了天下,确实是一个天才的创新。现在你该明白我前面回帖说的了吧。

科创服务器可能有bug了。回复了一个帖子,发现不见了。简单重写一下。

作者的原理图倒没啥错误。不过真正的关键信息不在原理图中。看了作者参考的论文,对这个设计佩服的五体投地。关键点是用xxxx加xxxx……

引用 虎哥:VNA作者的原理图会让人误以为所有的地都是实地。其实关键的信息就是有的地不是实地,是浮动的。信号通过巴伦,外套磁环,抑制了共模信号,于是同轴巴伦的电桥端其实只能走差模电流了。这导致电桥其实是被差动驱动的,而不是一端地一端信号地单端驱动。你说的对,这个设计起来细节着实很多。磁环的磁导率,高频响应,磁环套的位置,巴伦长度,同轴巴伦靠近电桥那端与地平面之间的空间关系都有影响。这个得是做过很多实验才能总结出来的。

出于好奇,昨天我还找群里的朋友扒下来看了一下。其实天底下少有新鲜事,这个构型在我看到的资料中都已经出来快四十年了,2015年还能在会议上发这种文章,这会议果然是来者不拒(也许是MICRAN公司对此有历……

引用 ddomax:单节的平行耦合线定向耦合器原理上就是窄带器件。相同PCB面积的情况下,电阻性器件...

hp778d专门把耦合线弄成斜线,然后上面盖阶梯状的介质,专门弄成不均匀的。

| 时段 | 个数 |

|---|---|

| {{f.startingTime}}点 - {{f.endTime}}点 | {{f.fileCount}} |

200字以内,仅用于支线交流,主线讨论请采用回复功能。