前言此方法可以将1个数字IO口,转化成1路模拟量输出,分辨率>14bit,信噪比>30dB

这样的指标,已经超过了一些古老的8位DAC例如DAC0832,也大大超过了PWM能实现的性能。

而且,这个方法对IO只有两个要求:

1. 至少要有几百k速度,一般单片机都有

2. 几个mA的推挽输出能力(没有则加上缓冲级)

端口数量不限,比如你可以把一个CPLD的几十个脚,统统变成DAC输出

![2012-11-03_19-28-23_265.jpg]()

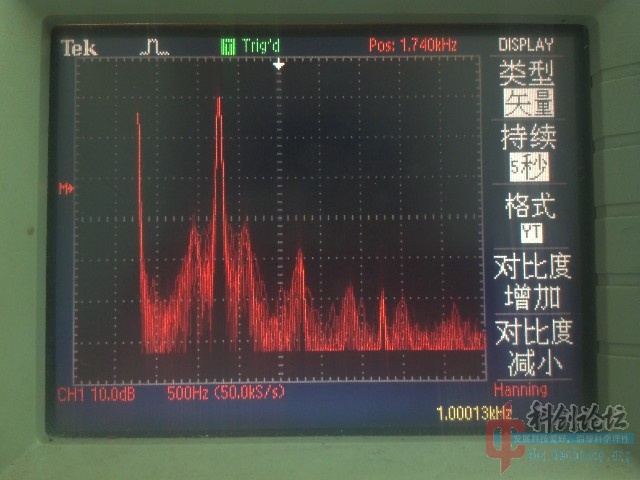

使用此法通过IO口回放1kHz 8bit 录音,并使用示波器进行频谱分析

![dsdemo2.gif]()

输出波形和频谱

实现方法构建一个一阶Delta-sigma调制器,伪代码如下,可选汇编或者verilog实现

int acc;

int output;

while(1)

{

acc += output;

GPIO = bit_C;//单片机ALU的溢出位

while(!timeout);

}

不断把输出期望值累加到一个寄存器中,如果加法发生溢出,则设IO为高,否则设为低。

模拟电路部分,需要给输出脚加个RC无源滤波,一阶或二阶都可以

IO---R---C---R---C---OUT

|______|_____GND

实际代码Verilog Code for Cypress PSOC3

// Generated on 08/27/2012 at 00:03

// Component: DSDDAC

module dac(clk,nrst,data,dout);

`define wl 17

input clk,nrst;

input [`wl-2:0]data;

output dout;

reg [`wl-1:0]acc;

always @ (posedge clk or negedge nrst)

begin

if(!nrst)

begin

acc <= 0;

end

else

begin

acc <= acc[`wl-2:0] + data;

end

end

assign dout = acc[`wl-1];

endmodule

实物测试无线音频传输装置,平台PSOC3,虚拟DAC时钟4M,SFDR > 30dB

DSDDAC.7z

10.43KB

7Z

76次下载

DSDDAC.7z

10.43KB

7Z

76次下载

![Screenshot from 2013-04-23 02:10:40.png]()

电路原理图,DSD_DAC为一个GPIO口,没有模拟功能

![2012-11-03_19-28-23_265.jpg]()

30dB是保守估计, 因为这里在1kHz附近的噪声,是录音音源和无线干扰引入的。

换成直接回放录音,SFDR可以轻松超过50dB。

此设计年代久远,未能留下最佳状态的数据,可惜了。

主观感觉,接耳机的时候,这东西音质类似AM收音机听本地强台的效果。底噪有点大,但是声音的还原还算不错

这个最主要优势是成本低,也没有PWM的基频泄漏,同时精度很高。

在这里输出级噪声和带宽的关系是“软”的,可以用更大噪声换取更大带宽。而PWM带宽受基波频率限制,提高基频频率之后,精度会严重降低。

原理这个算法是如何工作的呢?为什么它在有高带宽的同时,又有高精度?

其实,我们将上面的计算程序,变换一下形式,就很明白了

float diff = 0, output = 0.3;//output = -1.0~1.0 //0-1扩展到-1~+1

while(1) {

//diff+=output;

if(acc < 0.0) //diff = -acc

{ io = 1.0; }

else

{ io = -1.0; }

diff += io - output;

wait();

}

![6860566889445.gif]()

diff是输出的误差,输出会不断的在+1和-1之间摆动,努力使得误差为0;

这就相当于,diff是一个积分器,它对输出和期望的偏差量io-output积分。

而if语句则相当于比较器,如果积分器输出为正,说明输出太高,需要输出-1,反之需要输出+1

这样就会在引脚上产生一个方波,它的频率和脉宽不断变化,但是方波电压的平均值,正好等于output输出波形见文章开头那幅图

进阶如果采用更复杂的结构,例如使用4M的计数频率,3阶调制器,输出级采用对称恒流源结构(让IO口灌电流和拉电流的能力完全相同),理论上可以在4kHz内,达到80dB的信噪比。

从另外一个视角看上面的环路图:

量化噪声是在积分器之后,比较器(量化器)产生,输出端反馈回到积分器之前。

量化噪声通过负反馈环路,来到积分器之前。负反馈环路会抑制这个噪声。

积分器的存在,使得负反馈作用在低频段比较强,高频段比较弱(积分等效低通,引入一个极点,也就是20db/oct的滚降)

![320px-DeltaSigmaNoise.svg.png]()

结果就是,在最后输出的信号频谱中,噪声主要集中在高频部分

如果改变环路的传递函数,就可以获得不同的噪声成形特性,比如说带通特性

这个过程叫做噪声成形 Noise shaping(上图),噪声传递函数很重要。。。

提高内部调制器阶数,改用更先进的环路,在同样的调制频率下,性能可以成倍提高,但是计算分析也更复杂。

好在有现成的matlab工具箱可以完成调制器的设计:

XXXXXXXXXXXXXXXXX/matlabcentral/fileexchange/19-delta-sigma-toolbox反过来用那就是Sigma-Delta ADC~~~~高精度必然是它了~~~~

上面的工具箱可以用于分析ADC

胡思乱想如果把计数频率设计到1G、2G,甚至是10G、20G(很多FPGA的LVDS口已经有这个能力了),岂不是可以直接产生射频信号?

![Screenshot from 2013-04-25 09:19:53.png]()

REALIZATION OF A SIGMA-DELTA MODULATOR IN FPGA.pdf

561.43KB

PDF

247次下载

预览

REALIZATION OF A SIGMA-DELTA MODULATOR IN FPGA.pdf

561.43KB

PDF

247次下载

预览

ADC做到这个频率,又会怎么样呢。。。

吐槽digikey上面有不少24bit 96k音频DAC,信噪比超过100dB,还只要几块钱一个,它们就是这种原理做出来的。

相比之下传统的电阻阵列DAC,内部很复杂,成本很高,还只有极少数能做到16bit INL 1LSB误差,信噪比/谐波失真更是悲剧。

TI的器件页面上,16bit以上的DAC,全是D-S方式的。

废话D-S调制理论被认为是近几十年来模拟电路理论的最大进步,它模糊了数字和模拟的界限。

有时候,更简单的实现,反而带来更好的效果。。。。

Ref

XXXXXXXXXXXXXXXXXXXXXXX/wiki/%CE%94%CE%A3%E8%AA%BF%E8%AE%8A本坛大神Mitchell作品

XXXXXXXXXXXXXXXXXXXXX/XXXXXXXXXXXXXXXXXXXXXml闲来无事,搭了个简单的电路来验证Delta-Sigma DAC的性能。

滤波网络使用的最简单的无源2阶低通RC滤波器,DAC使用的100MHz时钟,Sigma累加器使用12bit分辨率:

![37_6688_7b313298bf96f6f.jpg]()

既然要来奇怪的波形,就来点更更更奇怪的波形吧,你看我Delta-Sigma DAC是怎么做得出来的,嘿嘿~

(1)奇怪阶梯。这相似度有没有99%?

![37_6688_bba48252492f415.png]()

(2)既然要YY,那就YY得更彻底一点。这细节够丰富吧?

![37_6688_51031f0cb407786.png]()

(3)挑战一下极限,XY显示。测试一下Delta-Sigma DAC的速度。

![37_6688_a1968980fcbccd3.png]()

再来点别的:

(1)100KHz正弦信号输出

![37_6688_1a406eea5f96c43.jpg]()

(2)Delta-Sigma信号波形。看仔细了,不是PWM。

![37_6688_c4246483902503d.png]()

(3)100KHz信号示波器截图。可以于LZ位的180Hz的正弦波做个对比。

![37_6688_0f069cc427e2d73.png]()

(4)最后是100KHz信号FFT,hanning窗。这信噪比没有60dB也至少有50dB了吧?单单这一项指标,就可以把加权电阻方案甩得不见踪影。

![37_6688_d146db4766a9168.png]()

200字以内,仅用于支线交流,主线讨论请采用回复功能。