方法当然还是有的。

在2011年2月28日

STEVE WARD更新了他的驱动原理图。

并命名为UD2.0 全称为Universal DRSSTC Tesla Coil Driver 2.0

version版本号后面跟的第一个数字发生变化

一般意义是主体构架发生了变化。

那么最大的变化在在哪呢?

![QQ截图20160722150151.jpg]()

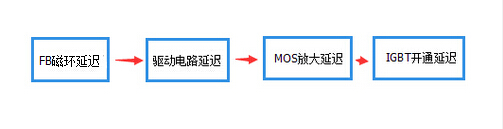

主要的变化在上图中有所体现。

简单分析电路原理:其改变主要是利用LR电路对输入的正弦波进行延迟,R3R4则对5V进行分压,产生一个约为1.6V的固定电压。这个固定电压经过IN4148钳位。最终输出一个叠加在1.6V直流偏压上的1.6V±0.3V与延迟后输入正弦波同频的方波。

这个方波与固定1.6V一同送入由TL3116精密比较器进行电压比较,最终送出0-5V的同频方波。

这个移相电路的原理非常容易理解。

由于TL3116非轨到轨的特性,必须加直流偏置,而较低的方波幅度,有利于提高速度,降低延迟。

TL3116拥有7.5nS的延迟时间,意味着信号电路最后输出延迟约为7.5+delayT。

这个时间经过输出Q和Qa反相。

可以巧妙的将延迟带来的时间,转换为提前移相。

为什么不可以通过UD1.3b驱动的方式进行反相应用呢?

原因很简单,如果这样,在第一个周期无法产生有效的正反馈,并且延迟不可调。

这个改进被应用于DRSSTC驱动电路是划时代性的。

其价值在于哪呢?

联系上文的两个应用情境

1:QCWDRSSTC 固定0.4uS延迟无法消除,那么就使相位提前0.4uS。

这样就完全抵消了IGBT和电路延迟等带来的负面影响。

损耗大大下降,能够把功率提到更高。电弧更长

2:使用模块的DRSSTC,1~2uS的固定延迟,使相位提前1~2uS,完全抵消延迟。

消除了尖峰,本来只能上到600V母线电压的DRSSTC可以运行在800V。

本来能运行在600A的电流可以运行在800A。电弧效果自然增加。

而相位补偿之后的电流-电压波形图如下。

![22.jpg]()

可以看到在电流最高的位置,由于相位补偿的存在,电压尖峰被几乎没有,取而代之的是非常干净的方波。

这个情况下,能达到的最大功率仅和流过IGBT的电流有关。

和尖峰带来的过压风险完全脱钩。

并且发热量大大减小,DRSSTC的体积也变得更小。

Q:UD2.x系列驱动适合应用于什么场合呢?

A:应用场合非常广泛,它在继承UD1.3b驱动能力的基础上,可以驱动大型IGBT模块,并且可以通过调节电感的方式,补偿系统延迟带来的尖峰、发热量大等问题。可以说从根本上解决了DRSSTC的最大损耗,和妨碍DRSSTC电弧做长电路方面的种种不利因素。

而频率应用范围,根据国外高压爱好者社区论坛的评测,工作范围在20KHz-1.1MHz均可正常运行。

是一款真正更加通用先进的驱动器。从功能上能够全面覆盖UD1.x系列的驱动电路。是替代升级的电路版本。

UD2.x系列的电路结构可谓是当之无愧的第二代DRSSTC驱动。

而UD1.3b是2008年的驱动版本

UD2.0是2011年的驱动版本

那么现在最新的DRSSTC驱动已经发展到什么程度了呢?

国外爱好者在做DRSSTC的时候,又会选用什么样的电路结构和驱动器型号呢?

在2011年2月28日

STEVE WARD更新了他的驱动原理图。

并命名为UD2.0 全称为Universal DRSSTC Tesla Coil Driver 2.0

version版本号后面跟的第一个数字发生变化

一般意义是主体构架发生了变化。

那么最大的变化在在哪呢?

主要的变化在上图中有所体现。

简单分析电路原理:其改变主要是利用LR电路对输入的正弦波进行延迟,R3R4则对5V进行分压,产生一个约为1.6V的固定电压。这个固定电压经过IN4148钳位。最终输出一个叠加在1.6V直流偏压上的1.6V±0.3V与延迟后输入正弦波同频的方波。

这个方波与固定1.6V一同送入由TL3116精密比较器进行电压比较,最终送出0-5V的同频方波。

这个移相电路的原理非常容易理解。

由于TL3116非轨到轨的特性,必须加直流偏置,而较低的方波幅度,有利于提高速度,降低延迟。

TL3116拥有7.5nS的延迟时间,意味着信号电路最后输出延迟约为7.5+delayT。

这个时间经过输出Q和Qa反相。

可以巧妙的将延迟带来的时间,转换为提前移相。

为什么不可以通过UD1.3b驱动的方式进行反相应用呢?

原因很简单,如果这样,在第一个周期无法产生有效的正反馈,并且延迟不可调。

这个改进被应用于DRSSTC驱动电路是划时代性的。

其价值在于哪呢?

联系上文的两个应用情境

1:QCWDRSSTC 固定0.4uS延迟无法消除,那么就使相位提前0.4uS。

这样就完全抵消了IGBT和电路延迟等带来的负面影响。

损耗大大下降,能够把功率提到更高。电弧更长

2:使用模块的DRSSTC,1~2uS的固定延迟,使相位提前1~2uS,完全抵消延迟。

消除了尖峰,本来只能上到600V母线电压的DRSSTC可以运行在800V。

本来能运行在600A的电流可以运行在800A。电弧效果自然增加。

而相位补偿之后的电流-电压波形图如下。

可以看到在电流最高的位置,由于相位补偿的存在,电压尖峰被几乎没有,取而代之的是非常干净的方波。

这个情况下,能达到的最大功率仅和流过IGBT的电流有关。

和尖峰带来的过压风险完全脱钩。

并且发热量大大减小,DRSSTC的体积也变得更小。

Q:UD2.x系列驱动适合应用于什么场合呢?

A:应用场合非常广泛,它在继承UD1.3b驱动能力的基础上,可以驱动大型IGBT模块,并且可以通过调节电感的方式,补偿系统延迟带来的尖峰、发热量大等问题。可以说从根本上解决了DRSSTC的最大损耗,和妨碍DRSSTC电弧做长电路方面的种种不利因素。

而频率应用范围,根据国外高压爱好者社区论坛的评测,工作范围在20KHz-1.1MHz均可正常运行。

是一款真正更加通用先进的驱动器。从功能上能够全面覆盖UD1.x系列的驱动电路。是替代升级的电路版本。

UD2.x系列的电路结构可谓是当之无愧的第二代DRSSTC驱动。

而UD1.3b是2008年的驱动版本

UD2.0是2011年的驱动版本

那么现在最新的DRSSTC驱动已经发展到什么程度了呢?

国外爱好者在做DRSSTC的时候,又会选用什么样的电路结构和驱动器型号呢?

200字以内,仅用于支线交流,主线讨论请采用回复功能。