量子兄弟,请教一下:

1.看了他的原理图和PCB实物,怎么感觉同轴巴伦的外皮和三个端口的地短路了呢?这样的话9.3欧的电阻R4不是被短路了么?

2.这个能将上图左边的也做成有右边一样的形成双向桥吗?

[修改于 7年8个月前 - 2017/04/14 20:19:32]

引用 虎哥:出于好奇,昨天我还找群里的朋友扒下来看了一下。其实天底下少有新鲜事,这个构型在我看到的资...

量子兄弟,请教一下:

1.看了他的原理图和PCB实物,怎么感觉同轴巴伦的外皮和三个端口的地短路了呢?这样的话9.3欧的电阻R4不是被短路了么?

2.这个能将上图左边的也做成有右边一样的形成双向桥吗?

引用 量子隧道:关于这个电桥,有一点很蹊跷:按理说,电桥的输出(反射信号的提取)应该在R3的两端,不...

虎哥也帮忙看看,能否解答一下蒙新的疑问?

看了作者的定向桥,两边打过孔到地,内层的地联通的,这不是等于把9.3欧的电阻R4短路了么?

还有就是能否如下图做成双向桥?

量子兄弟,请教一下:1.看了他的原理图和PCB实物,怎么感觉同轴巴伦的外皮和三个端口的地短路了呢?这...

低频短路。高频(GHz)不短路。因为通过pcb挖空导致产生了环路(同轴线的皮和挖空外围的PCB地围成了环),高频阻抗很大。

同轴线上套磁环,可以把低频不短路的频带向下延伸,延伸到MHz或百kHz级别。

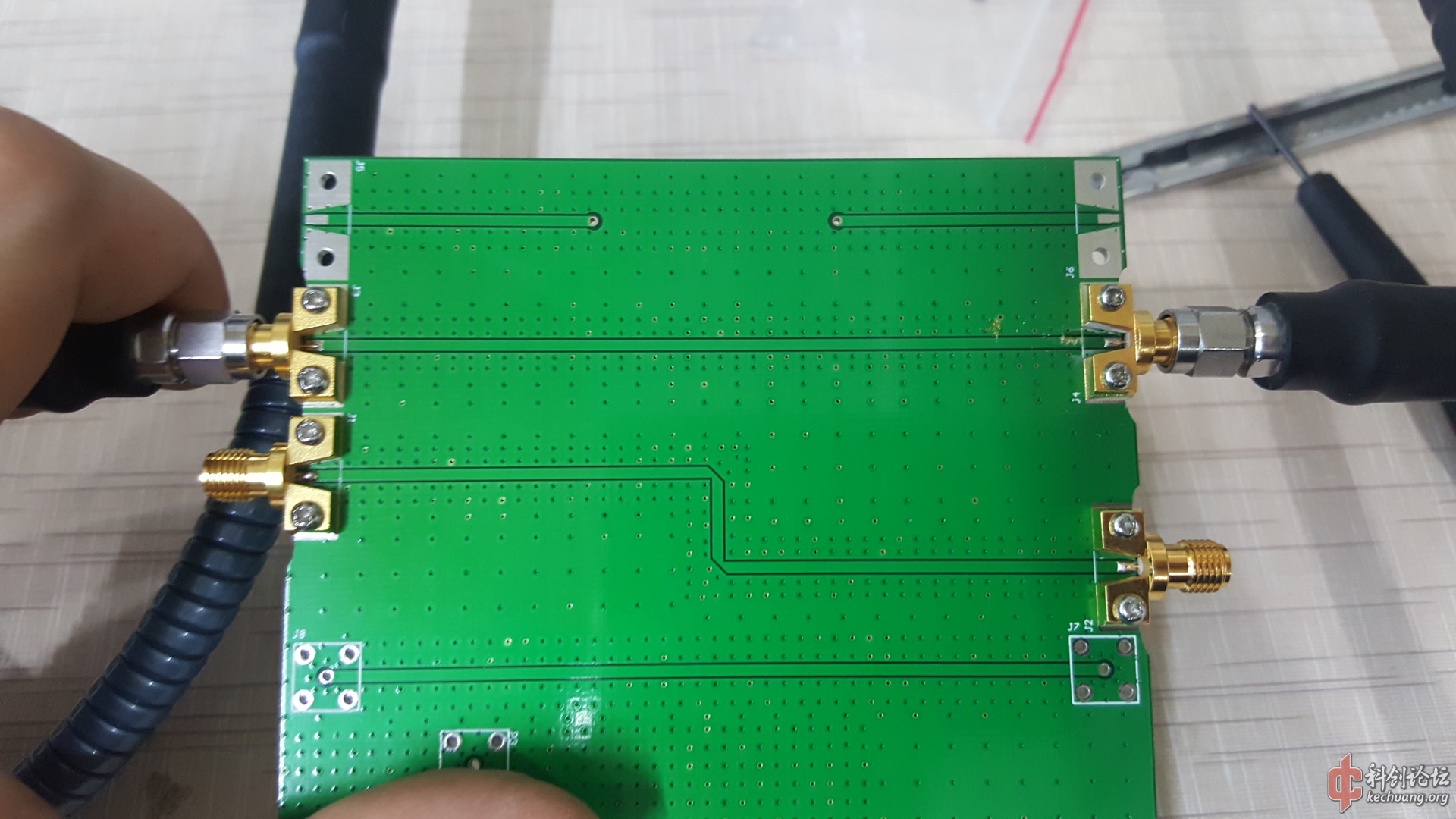

另外,双向桥的做法,我正是这么做的。据说啊,PCB挖空部分里的那根同轴线,中间某个地方的皮,需要和PCB焊接到一起。不过我没这么做,好像也work。

工作了一年多,拿个仿真项目跟虎哥分享一下处理射频信号的部分PCB设计:项目是一个12G 的信号,PCB设计上主要做了几点:

走线避免过孔,拐角采用圆弧的方式,最大程度保证每一小段线宽一致,避免阻抗的变化

信号线连接接插件的焊盘底层需要适当挖空(焊盘与连接器间有焊锡,会降低阻抗,挖空焊盘增加平面间距离把阻抗进行补充,避免强烈反射)

传输线中如果串阻容器件,也需要挖反焊盘,原理同上

用原理图简单展示一下,希望对设计提供帮助

连接器的反焊盘直接挖到底;串联电容的反焊盘挖了一层,参考第三层地。

同时足够的过空保证了回流顺畅。

关于过孔对阻抗的影响可以参考一博的这个文章,一博的好多技术文章含金量很高,浅显易懂:XXXXXXXXXXXXXXXXXXXXX/cn/TechnicalArticle/XXXXXXXpx?id=1255

跟一博交流过,前些阵子他们设计过56G的背板,行业内算很NB了,不止过孔,哪怕高密接插件的的压接孔都设计-仿真-验证 来来回回好几次。

工作了一年多,拿个仿真项目跟虎哥分享一下处理射频信号的部分PCB设计:项目是一个12G 的信号,PC...

关于连接器下面挖空的事,射频连接器在设计时就已经考虑了阻抗匹配问题,务必按手册使用,不可自行挖掘。可能您遇到的是用普通连接器或低频连接器超频到高频使用的情况,有可能挖空有益。不过在射频电路特别是仪表电路中,是不允许随意“创造”的,没有合适的连接器,就先设计连接器。如果要挖,挖几层,挖多大,都是要仿真确定,实验验证的。

射频电路一般要求焊盘和线路等大或略小,如果大了可以在线路上补偿。其实更主要的问题是器件封装不适宜高频,比如普通的电阻电容,封装的分布电容和电感都大,而且还不知道究竟有多大(除非专门为高频设计的),挖空下层确实是一种巧妙的办法,特别是找不到或者因为成本问题不想用专门器件的场合。

低频短路。高频(GHz)不短路。因为通过pcb挖空导致产生了环路(同轴线的皮和挖空外围的PCB地围成...

感谢回复呀,现在基本明白了,最近看了下文献,也没看到有需要把中间接地的呀,而且我看了作者的实物也没接地嘛,另外对磁环的选型,量子兄弟有研究吗?我看了文献,原则是阻抗最好大于1M,那么我要实现低于10M的频率,那我的磁导率u不就得选得至少45000了么?据我查找貌似像老外那个尺寸应该是没有这样的磁环的吧

低频短路。高频(GHz)不短路。因为通过pcb挖空导致产生了环路(同轴线的皮和挖空外围的PCB地围成...

还真是的,我看了一个专利,确实是中间接地,估计是为了对称的吧,他为了两边对称各放7个磁环

| 时段 | 个数 |

|---|---|

| {{f.startingTime}}点 - {{f.endTime}}点 | {{f.fileCount}} |

200字以内,仅用于支线交流,主线讨论请采用回复功能。