最新进展:东磁答应免费帮我做一套DMR96材料的磁芯样品,预计四月中旬开始调试整个电路。

众所周知LLC拓扑由于可以实现初级侧ZVS和次级侧ZCS,是高频高功率密度开关电源的常用拓扑,特别是SiC和GaN普及之后。而三相交错的好处是可以降低输入和输出电流纹波,进一步减小滤波电容的体积。如果把三个变压器集成在一起可以进一步减小体积,降低磁损,可谓一举多得。

在IEEE上看到了一篇很有意思的paper,来自CEPS,介绍了三相磁集成LLC的几种新型磁结构:IEEE Xplore Full-Text PDF:

比较详细地分析了各个接法的优劣势,主要从变压器伏秒积和电容直流偏置等角度来比较。

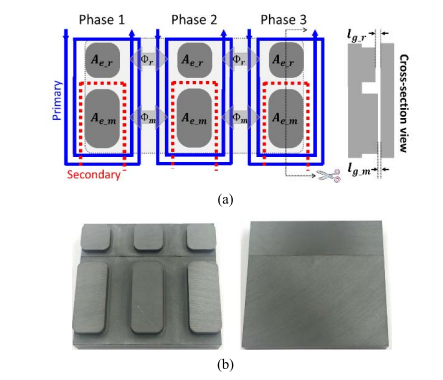

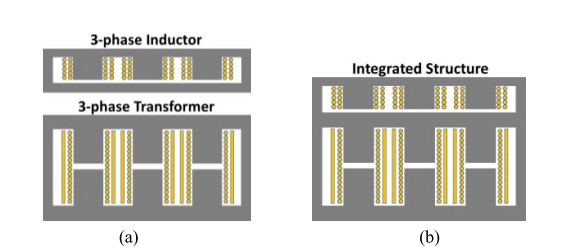

而重头戏是磁集成方法,主要有两种:

由于第一种比较适合做成PCB winding,本科毕设决定复刻第一种。

小磁柱只绕过初级绕组,这个是为了产生漏感Lr的,调节这个区域的磁芯气隙可以调节Lr。

大磁柱是产生Lm(励磁电感)的,留气隙是为了让励磁电流足够大来在死区时间内抽走Cgd上的电荷,这个可能也是需要微调的。

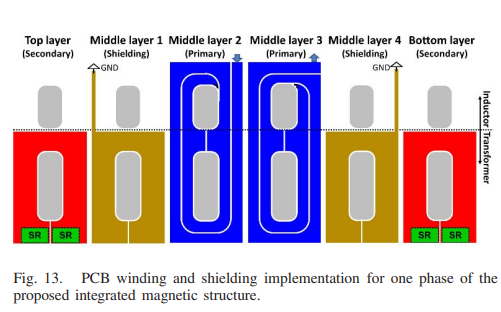

论文中给出了用单6层板实现这个PCB winding的参考结构:

由于开关频率很高(1MHz),PCB Winding之间的电容影响比较大,所以加入了屏蔽层。屏蔽层中间接地,这样和次级线圈之间的电压分布可以使共模电流抵消。初级2+2,次级1并1,匝比4:1,谐振状态下变换器总变比8:1

如果三相LLC采用公共点不接地的方法,那么该接法可以实现一定程度的自动均流(Lr和Cr类似于多电源并联时均流电阻的效果)

接下来介绍一下我的方案:

设定功率1kw,输入电压400V,输出电压24~60V,频率500KHz。由于电压范围有点宽,所以干脆后面加了个三相交错buck,前级LLC工作在准谐振状态,调试也会简单一些。buck使用电压外环-电流内环的控制策略均流,所以又加了三片30A的霍尔电流测量。

写了个脚本简单优化了一下变压器损耗(史坦敏茨公式估算磁损,dowell模型估算绕组交流电阻系数),得到的关系图如下:

固定每一相宽度为24mm(两个To220管子的宽度大概是这么多,方便布局),对每一个变压器长度值,优化绕组区和磁芯区占据空间的关系使之损耗最小。(绕组宽了铜损会降低,相应Ae小了磁损会增大,存在一个总损耗最小的值)也就是说这个图是每一个length下的最小损耗扫描结果:

![WNZ~HLJD%9T$}%$H9]6$)1W.png](https://img.kechuang.org:81/r/340959?c=resource)

最后选择的设计长度是30mm。

有了这些之后开始做联合仿真,使用Ansys旗下的simpolorer和Maxwell联合仿真,先画了一个CAD导进去:

在simpolorer里搭好其他部分的电路,在Maxwell里设置好求解域,边界条件和激励添加的端子。

损耗仿真的结果:

铜损比简单估算的结果大了不少,不过勉强可以接受,可能是之前没算励磁电流的影响进去。

上电过程:(不在谐振频率)

![7O~X}_%7]_V8`YV_`F@{LUV.png](https://img.kechuang.org:81/r/340963?c=resource)

稳态的时候:(在谐振频率上)

虽然仿真的时候各相Lm的差值足有20%,但最终电流差值并不是很大,我选择的是△-Cr+Y-primary结构,似乎确实有一定的自动均流效果。

接下来开始搭实物

PCB六层板画了一个多星期,好累。(这是刚走完功率部分的样子,MCU用的STM32G474VET6)

![MN]L}}F_(L0UJRUFRRA4WNV.png](https://img.kechuang.org:81/r/340969?c=resource)

高压侧6只SiC MOS,整流管6只GaN,buck使用普通MOS(开关频率降到100K)。

目前板子刚到,还在和定制磁芯的厂家拉扯(电子邮件沟通效率有点低),其他器件有的从美国发的也还没到,希望后续一切顺利。

等开始调试会继续更新

200字以内,仅用于支线交流,主线讨论请采用回复功能。