坐等套件

加载中

加载中

表情图片

评为精选

鼓励

加载中...

文件下载

加载中...

[修改于 10年7个月前 - 2014/11/12 06:22:16]

引用 rpg-7:其实也不排除CPU0使用中断,这个精简CPU可以弄成中断堆栈版, 增加延迟和硬件开销, 这个东西两面性,

我倒是想,加入中断机制后,是否可以利用中断来实现公用RAM的数据定向传送?我YY大致是:除非下位机被中断,否则一切情况下不允许读写公用RAM,上位机写数据,向特定CPU发送中断信号,通知它读取数据,当任意下位机完成计算后,只有中断主机,然后...

引用 kknd:进度正在推进中[s::victory:] 最后2.5片 准备封顶[s::$]

坐等套件

引用 rpg-7:!~ 得研究看看

突然灵感咋现!楼主知道VMP壳吗?就是把win32程序转换成一个虚拟的很简单的CPU里跑的程序,来增大代码量,我在想如果把vmp的机器码换成你小UU的指令,把小UU弄成32位的。。。啧啧啧。。。。

引用 神之觉醒:哈哈。。。不过这个其实有难度,毕竟是win32下的,还是要调用api的。。。。不过也许可以直接转换机器码。。。那就爽了

!~ 得研究看看

引用 小八一3:打板打板~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

我天天来看大神的进展

引用 rpg-7:什么段寄存器堆栈寄存器...EAX EBX... 可以把内存单元定义为那些寄存器 然后用本CPU的指令组合..实现大部分~X86指令功能~~ 这样一看 怎么感觉X86倒像高级语言了+ + 说实在的用指令模拟X86实现X86指令功能 可能比C语言生成的代码还麻烦, X86指令集相当于高级语言了。。。里面的变址寻址相当于C语言的数组操作。。。还有CALL。。IO操作也有专门的指令 全部硬件实现[s:;P] 攻城量庞大。 堆硬件堆得够猛。 估计设计X86的攻城师刚饮左两杯二锅头 才有这个劲

哈哈。。。不过这个其实有难度,毕竟是win32下的,还是要调用api的。。。。不过也许可以直接转换机器码。。。那就爽了

引用 rpg-7:现在想想 觉得这样搞复杂指令, 增加一个核心, 就相当于增加一个很臃肿的硬件, 功耗也大...可能内核不是功耗大的原因,, 也许是缓存? 缓存占晶体管数量也比较可观, 现在我这样搞可能没有频率优势.. 但是可以有办法增加处理单元并行处理一个任务, 比如解码播放视频, 一个CPU解,解好的二进制数据放内存或硬盘, 然后另个CPU再把解好的二进制数据读出来刷屏, 一个CPU解速度不够可以2个CPU 2个CPU不够可以3个CPU.......[s:;P] 我这个CPU现在用74搭, 目前内存还不是瓶颈, 要是内核速度比内存快就要上缓存了噢.. 不担心速度, 对影响速度的应该~运算器.

哈哈。。。不过这个其实有难度,毕竟是win32下的,还是要调用api的。。。。不过也许可以直接转换机器码。。。那就爽了

引用 rpg-7:算了一下缓存占多少晶体管, 假设一位6个, 8位48个, 1KB 49152个, 1MB 5千万个[s::funk:] 还有地址译码逻辑??&&&&(?...

哈哈。。。不过这个其实有难度,毕竟是win32下的,还是要调用api的。。。。不过也许可以直接转换机器码。。。那就爽了

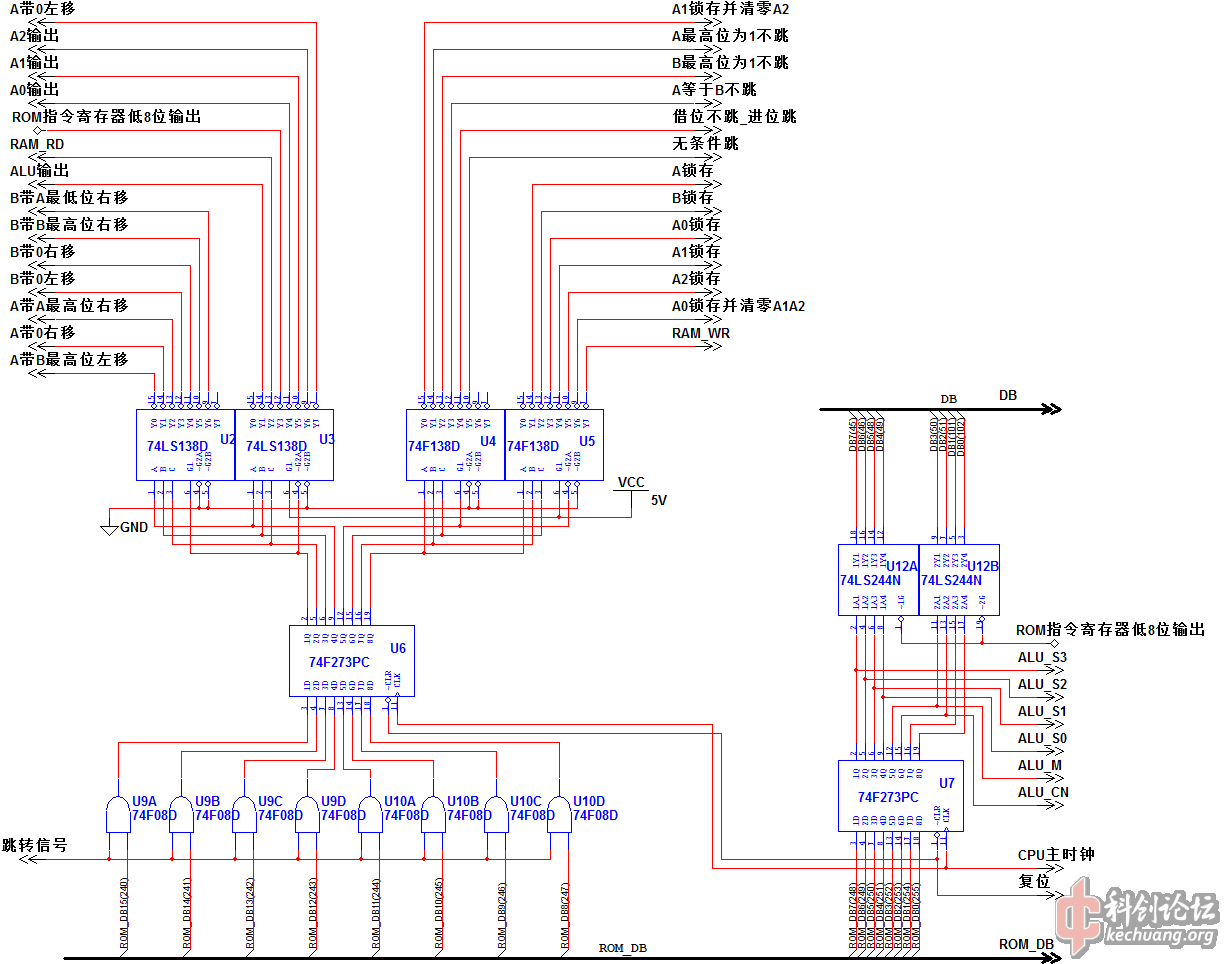

引用 分立元件:那我解释一下本贴CPU执行指令的本质原理.

被大神吸引过来论坛,能讲解一下控制器原理吗?我看了“编码的奥秘”和“穿越计算机的迷雾”两本书,其它的都明白了,就是对控制器内部实现的原理不是很明白!

引用 nqmtlove:多谢关注... 整机电路板文件已经丢到工厂里面了 估计过几天到手.........

关注好久!快出套件!!!

引用 rpg-7:差不多 真的很简单...

变址寻址?是间接寻址的一种吗?我这东西是不是和跳转类似?CPU结构这块我没学过。。。不过 。。貌似这玩意您给搞得巨简单。。。极端简单指令集?

引用 小八一3:...测试OK先[s::victory:]

终于大板了要一套

引用 rpg-7:好主意...

对了,要不这机子试试用铁电存储器吧!ROM/RAM合一如何?还有,其实我认为16位的也值得一搞,不过最好用贴片元件。。。

引用 rpg-7:用FPGA速度吊.. 搞大机方便... 不过现在简单的电路就不麻烦FPGA了, 这样运行起来比较有"松香味"[s:;P]

还有,我个人真心建议楼主可以上FPGA了。。。。想要啥直接用语言描述仿真,方便的多。。。而且还有实用化的希望。。。

引用 神之觉醒:所有控制信号同时打开???电路的确是简单了,直接译码就可以了!以前我还以为是顺序打开的呢!搞的自己设计好复杂!

那我解释一下本贴CPU执行指令的本质原理.

往常的CPU设计每种指令都有一个指令前缀码, 比如0001代表传送 0010代表运算 0011代表跳转...

但是本贴的CPU不是按照这个理念搞, 没有指令前缀码, 因为这样搞对硬件来...

引用 神之觉醒:不过,我在想,弄片FPGA,在上面堆个十几片32位的。。。中间弄一缓存。。。直接实用化,赶英超美[s::lol]

用FPGA速度吊.. 搞大机方便... 不过现在简单的电路就不麻烦FPGA了, 这样运行起来比较有"松香味"

引用 rpg-7:有这个意思~~![s::funk:][s::$][s::lol] 后面四个字不敢保证[s::shutup:]

不过,我在想,弄片FPGA,在上面堆个十几片32位的。。。中间弄一缓存。。。直接实用化,赶英超美

引用 rpg-7:多个运算器寄存器^%^*&^控制,指令位宽可能几十上百几百位, 这回好玩. 不能搞太猛 要低调[s::lol][s::L]

不过,我在想,弄片FPGA,在上面堆个十几片32位的。。。中间弄一缓存。。。直接实用化,赶英超美

引用 rpg-7:

不过,我在想,弄片FPGA,在上面堆个十几片32位的。。。中间弄一缓存。。。直接实用化,赶英超美

引用 神之觉醒:要是这样的话那指令要有多长啊~

某SRAM存储器的写时序.. tAS 0纳秒,,, 意思说给地址的同时可以写线拉低.. 看来内存地址都可以放在指令里面.. 这么一来内存都可以像寄存器一样操作

引用 神之觉醒:作为梦想未尝不可,最终和parallax公司齐头并进如何?[s::lol][s::lol]不过,缓存分组如何?主CPU允许读写全部,但是从CPU只允许读写自己的640kb?

某SRAM存储器的写时序.. tAS 0纳秒,,, 意思说给地址的同时可以写线拉低.. 看来内存地址都可以放在指令里面.. 这么一来内存都可以像寄存器一样操作

引用 小龙:估计长到月球去了[s:;P] YY一下

要是这样的话那指令要有多长啊~

引用 rpg-7:

作为梦想未尝不可,最终和parallax公司齐头并进如何?不过,缓存分组如何?主CPU允许读写全部,但是从CPU只允许读写自己的640kb?

引用 神之觉醒:缓存控制器不可以分组使用吗?我又想到一个了:是否可以用中断和定时器来实现循环结构?省去循环体变量+1的那个机器周期,我YY一下:循环程序写计算机器周期数,将数字写入定时器寄存器,将使能位 置1,开始计算,到达时间后,中断处理程序结束计算?貌似不是个太好的注意╮(╯▽╰)╭ 。。似乎按这个结构,以存储器的存取方式,数个CPU一旦同时要求内存,就绝对要排队了。。。对了,还有,可不可以在缓冲控制器里用一个累加器,加法器和对比,将内存初始地址扔进加法器的一组,累加器另一组,加法器输出接到接到内存地址线上,一个时钟累加器加一输入加法器然后加法器输出和预定地址对比,同时累加器输到缓存的地址线,缓存数据线和内存地址线相连,一个时钟装一个字节,对比到达定好的地址锁死累加器,等待CPU运算完成后再次调用,写内存同理,然后,CPU一边算着,缓冲区继续一个时钟装一个字节,爽得一塌糊涂,而且我还想,若CPU要读取不同

不纠结那个...内存不好管理/.. 有另一个结构..内存比较好管理, 缓存控制器的作用是....CPU需要的数据超出缓存的范围后CPU刹车, 然后缓存控制器再从内存取一块数据装进缓存里面, 然后CPU继续运行, 那个偏移量寄存器应该放在...

引用 神之觉醒:同时给数个缓冲区装数的话,可不可以靠流水线实现?预先运算,存放,到最后直接出结果,或者直接主CPU把那些乱玩意儿甩给从CPU干╭(╯ε╰)╮,然后流水线直接从公共缓冲区中读出运算出来的指令和数据

有这个意思~~! 后面四个字不敢保证

到时打算每个可能CPU里面装几个运算器, C语言里面的多元式一条指令搞定...也不是一条指令...要给N个寄存器装数~~~ 然后一个卡擦结果就出来~~~~搞费

给N个寄存器装数比较耗时间, 如果...

引用 rpg-7:YES!!! 差不多是这个意思, 输入时钟极限周期和这些器件延迟总和有关(累加器延迟+加法器延迟+比较器延迟+两个门的延迟).

俺的想法是这样的哈,一个时钟过三态门,累加器+1,累加器数据和锁存的地址数据相加,累加器的地址就送给缓存的地址线,缓存的数据线通过三态门和内存数据线相连,缓存的读写使能线拉高,写,内存的拉低,读。加法器送出来的地址一边进内存,一边进同或门,...

引用 大胆哥:马上又要吹个牛逼

又上来看楼主吹牛逼了

引用 rpg-7:。。。话说。。似乎又想到有个新结构可以让CPU大部分时间全频工作不受内存延迟影响,不使用缓存,如果搞成功的话。。 该不该公开。。。@大胆哥

俺的想法是这样的哈,一个时钟过三态门,累加器+1,累加器数据和锁存的地址数据相加,累加器的地址就送给缓存的地址线,缓存的数据线通过三态门和内存数据线相连,缓存的读写使能线拉高,写,内存的拉低,读。加法器送出来的地址一边进内存,一边进同或门,...

引用 神之觉醒:应该早公开,但有公开的技巧。

。。。话说。。似乎又想到有个新结构可以让CPU大部分时间全频工作不受内存延迟影响,不使用缓存,如果搞成功的话。。 该不该公开。。。@大胆哥

好像不管怎样CPU速度都要受制内存

引用 虎哥:老虎建议很不错~~~!。要是搞出来 这个新结构名称可能是《KC-LS分散内存阵列变频执行结构》 名称很N的样子 看名称应该就知道大概。[s::lol] 这个结构即使使用100ns(10MHZ)的指令存储器,CPU的速度也不会受制于存储器,用高速门电路搭跑上百M~~~[s::lol]

应该早公开,但有公开的技巧。

1、要清楚新结构在业内的水平,看看前人有没有做过类似的或相同的。

2、要给新结构取个容易记住的名字,比如龙少结构。

3、公布以后要加以宣传,最好是平面媒体。每次楼主发的结构,KC都用微博等渠道推过。但是如...

引用 神之觉醒:我猜猜。。。变频执行靠除法器实现?给不同的设备不同的时钟,但是同步怎么办?

老虎建议很不错~~~!。要是搞出来 这个新结构名称可能是《KC-LS分散内存阵列变频执行结构》 名称很N的样子 看名称应该就知道大概。 这个结构即使使用100ns(10MHZ)的指令存储器,CPU的速度也不会受制于存储器,用高速门电...

引用 rpg-7:[s::lol] 理论阶段~ 硬件延迟高的指令低频 ,硬件延迟低的指令高频, ~ 内存分散成多组, 不连续对同一组操作就可以提高速度... N通道. 要是连续对同一组操作就降频.. 好像这样搞又很麻烦

我猜猜。。。变频执行靠除法器实现?给不同的设备不同的时钟,但是同步怎么办?

引用 表慌张:不算先进~ 玩具水平, 多任务需要中断的系统可能上不了 [s::lol] DOS差不多的就可以上

先进,,,不明觉厉 国产有个打酱油操作系统 移植过来呗。

。。

。。

200字以内,仅用于支线交流,主线讨论请采用回复功能。