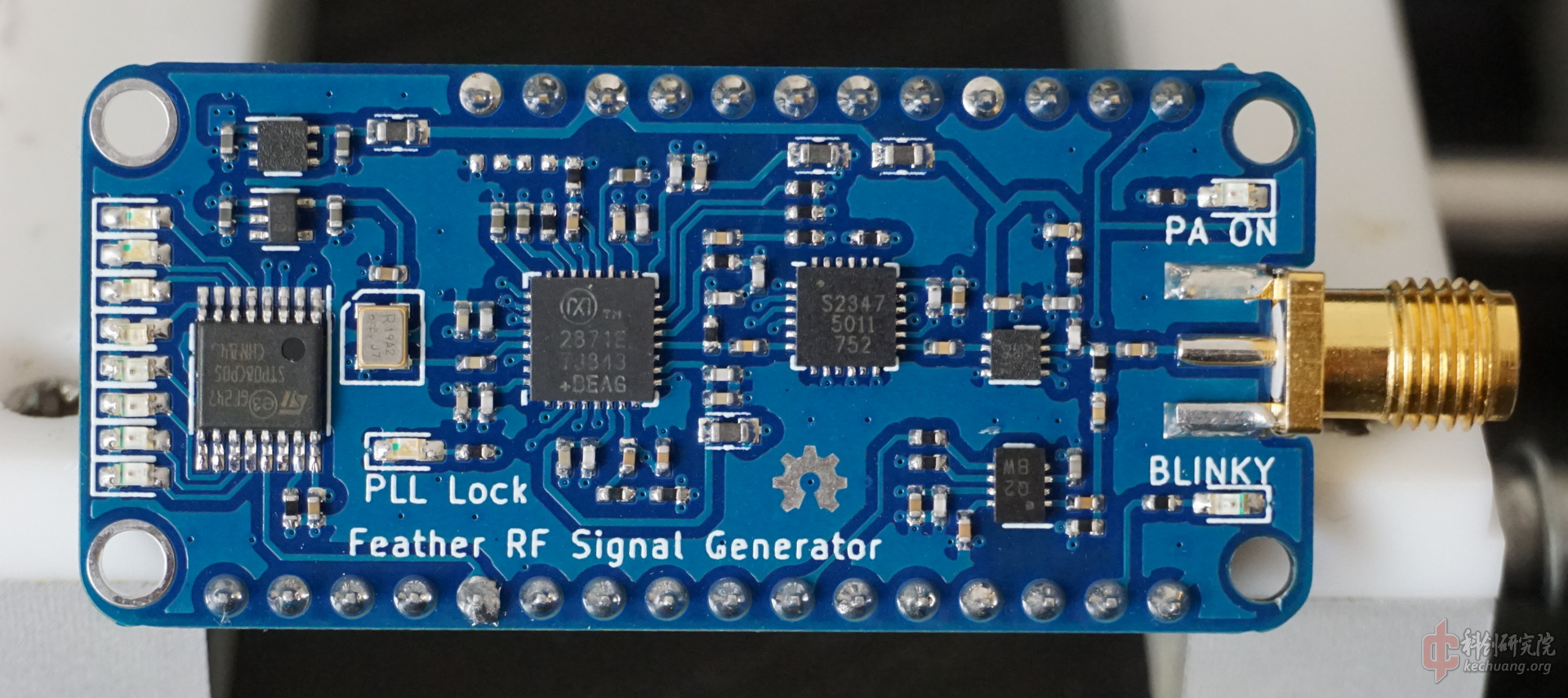

这个没有滤波器组,低频全靠分频,谐波很大的哦.

这个追求的是简单,便宜,方便。别对指标有太高期望,除了楼上说的低频谐波,相噪也不会太好。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

这个追求的是简单,便宜,方便。别对指标有太高期望,除了楼上说的低频谐波,相噪也不会太好。

实在不懂了,请教一下。为什么在低频会有谐波,按理说无论高低频都是锁相环的vco输出的正弦波,为何偏偏在低频段谐波增大

200字以内,仅用于支线交流,主线讨论请采用回复功能。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

分频器以后就是方波了,锁相环只能工作在有限的频段

感谢回复,仔细看了下手册,这颗芯片的射频输出是open collector的,低频下实际输出接近方波,看来想低频下谐波少,得找其他合适的芯片或者外置需要外置vco的芯片自己搭了。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

貌似这里对信号源有需求的,要么不在乎买一个,要么自己画一个。。。

因为信号源的可玩性实在不怎么样,所以在爱好圈里的处境比较尴尬,如果是刚需的话,就有一些特别的要求,比如要能衰减到很小很小(-130dBm)。

低频一般用混频的办法产生,信号质量会好得多。VCO一般最多覆盖一个倍频程,用来拼低频过于麻烦,除非有特殊要求一般不会这样做。

现代信号源低频也可以用DAC直接产生。

楼主可以自己画,用个STM32开发板来控制。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

这个PLL我常用,做本振源,谐波比较大,窄带用的话要加滤波器滤除2、3、4次谐波,寄存器配置方面和ADF4351类似

200字以内,仅用于支线交流,主线讨论请采用回复功能。

请教一下,加滤波器组的话,频段一般怎么划分?

要求不高的话。。。VCO工作段可以不加,然后逐级串联,一个倍频加一组,三四个搞到个几百兆左右应该差不多了。低频还是混频吧。哪怕加了滤波器,你的端口还得要ALC来控制幅度。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

这个PLL我曾经用来D过VNA,即网络分析仪。

频率覆盖粒度还是不错的,因为有分数分频。

低频输出基本上是方波。

输出是OC门,板级偏置电路处理不好的话,在4-6GHz有10dB量级的塌陷(当然也不排除是因为我的FR4烂板高频不行带来的)。这个我一直没定位出原因。

最终做出来的VNA,动态范围只有60dB。影响动态的地方主要是在输出分频系数切换的点(也就是每两个倍频程的衔接处)。在每个倍频程之内,还是可以做到70-80dB的。当时猜测衔接处动态范围降低的原因是功率突变和波形突变(因为切换了输出分频器)。因为我后面又有其它兴趣点了,就搁置了,没继续改进。

貌似也见到过有用它做FMCW雷达之类的东西的。不过有些PLL内带分频系数自动计数,比它更适合做FMCW。

200字以内,仅用于支线交流,主线讨论请采用回复功能。

想请教下,这里的低频大致是什么范围?

ADI的AD9951-AD9956, 都是14bit 400Msa DDS, 做到200MHz以内的正弦波输出没问题

还有更高频率上G都有,不过价格贵的没朋友

200字以内,仅用于支线交流,主线讨论请采用回复功能。