引用 kknd:....希望不出错误 还剩几片先 画完花1天时间检查. 套件测试好了我再开淘宝链接[s::lol][s::handshake]

期待!第一时间预订一套,请给价格和付款方式。楼下保持队形

68167

%7B%22isLastPage%22%3Afalse%2C%22notes%22%3A%5B%5D%2C%22pid%22%3A%22t68167%22%2C%22tid%22%3A%2268167%22%2C%22mainForumsId%22%3A%5B%22211%22%5D%2C%22categoriesId%22%3A%5Bnull%5D%2C%22tcId%22%3A%5B%5D%7D

%7B%22isEditMode%22%3Afalse%7D

龙少精简嗨爆版8位单周期CPU内核原创电路发布(计划出套件)

刚画完电路先把电路贴出来[s::victory:]

这个CPU由30多片TTL门电路组成.

非常简单而强大的电路...连我自己都被这个设计震惊...[s::funk:][s::@]

设计是按照硬件条件来设计的, 计划装在两片10CM*10CM的PCB上面,这个规格的PCB打样价格低.

跳转指令跳转消耗2个时钟,不跳转消耗1个时钟,其他指令1个时钟.

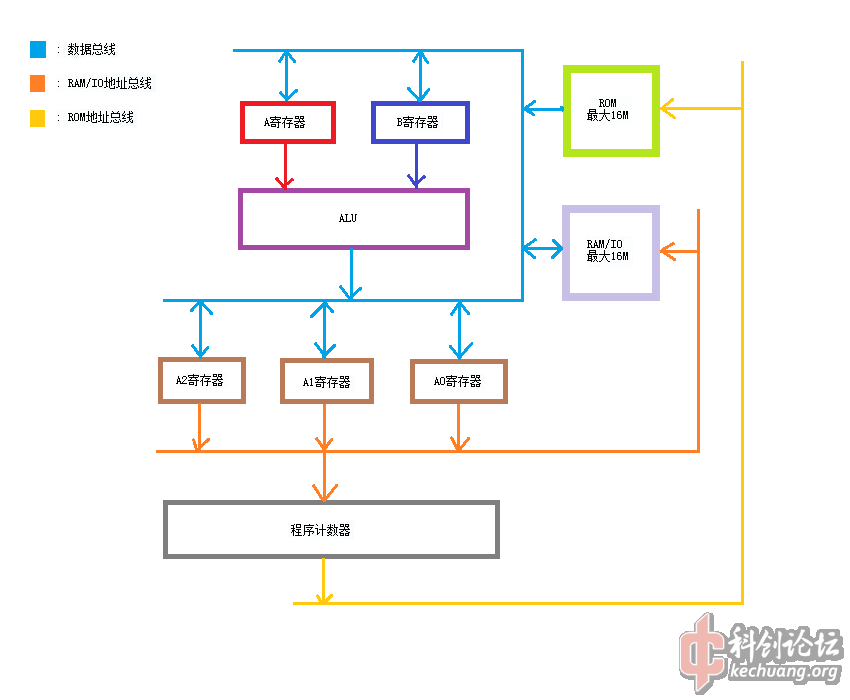

RAM和ROM地址为24位(地址寄存器24位,程序计数器24位),最大可以寻址16MB的RAM和16M的ROM.

IO方式为内存映射IO.

保守估计用同样型号的IC性能大概比小UU强大约2倍,条件是频率要运行在10MHZ左右(性能相当于小UU运行在27MHZ的2倍), = =其实性能要看每秒加法减法多少次...[s::L][s::lol] 看频率有点吹水的感觉[s:;P]

Multisim 11.0仿真文件下载:

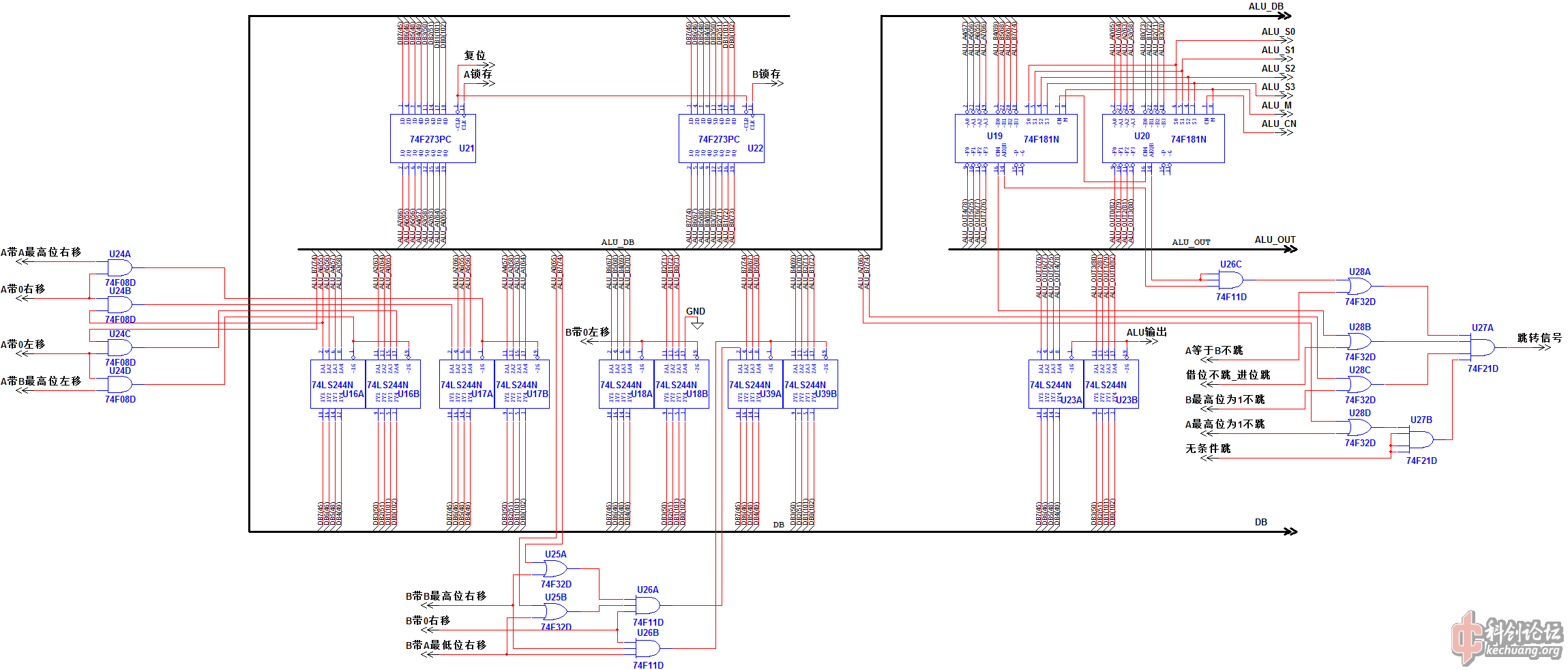

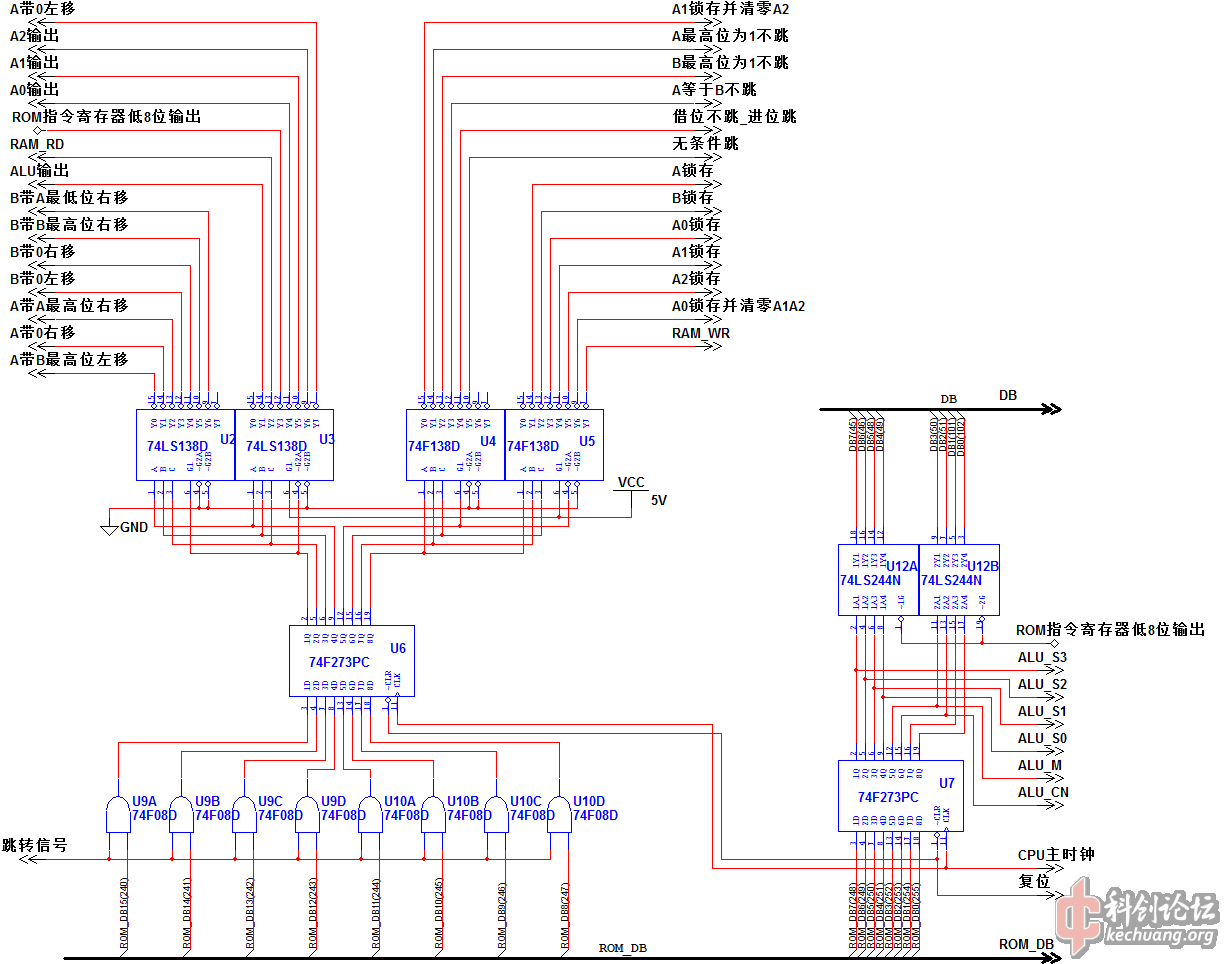

本CPU可以看成由3个部分组成;

1.运算逻辑.

![龙少精简嗨爆版8位单周期CPU运算逻辑.png]()

2.地址逻辑.

![龙少精简嗨爆版8位单周期CPU地址逻辑.png]()

3.指令译码逻辑.

![龙少精简嗨爆版8位单周期CPU译码逻辑.png]()

数据通道结构图:

![龙少精简嗨爆版8位单周期CPU结构.png]()

这个CPU由30多片TTL门电路组成.

非常简单而强大的电路...连我自己都被这个设计震惊...[s::funk:][s::@]

设计是按照硬件条件来设计的, 计划装在两片10CM*10CM的PCB上面,这个规格的PCB打样价格低.

跳转指令跳转消耗2个时钟,不跳转消耗1个时钟,其他指令1个时钟.

RAM和ROM地址为24位(地址寄存器24位,程序计数器24位),最大可以寻址16MB的RAM和16M的ROM.

IO方式为内存映射IO.

保守估计用同样型号的IC性能大概比小UU强大约2倍,条件是频率要运行在10MHZ左右(性能相当于小UU运行在27MHZ的2倍), = =其实性能要看每秒加法减法多少次...[s::L][s::lol] 看频率有点吹水的感觉[s:;P]

Multisim 11.0仿真文件下载:

本CPU可以看成由3个部分组成;

1.运算逻辑.

2.地址逻辑.

3.指令译码逻辑.

数据通道结构图:

[修改于 10年2个月前 - 2014/11/12 06:22:16]

加载全文

引用

引用 kknd:OK~~~感谢这么大力的支持[s::kiss:]

我没办法经常关注这里,请一定帮忙留下一套,不要卖光。我一定要

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

既然这么多人支持... 那我就谈一下意YIN的超级嗨爆大型机原理... 很简单..

一个CPU运行一个任务, 图里面的CPU0运行的是操作系统 就是用户层面的, 后面几个CPU1~CPUN是后台层面的...然后...你懂的

整个系统不需要使用中断...个人认为中断简直就是CPU的噩梦 不能增加处理能力 而且还要消耗一堆硬件...

![多核并行机大概构构图.jpg]()

一个CPU运行一个任务, 图里面的CPU0运行的是操作系统 就是用户层面的, 后面几个CPU1~CPUN是后台层面的...然后...你懂的

整个系统不需要使用中断...个人认为中断简直就是CPU的噩梦 不能增加处理能力 而且还要消耗一堆硬件...

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:没错..中断一个是为了快速响应外部设备然后传数据,另一个是实现一个CPU运行多个任务... 自从YY出新结构,CPU硬件电路已经不再复杂, 打算堆一大驼CPU上去, 没用到的核心就关闭电源, 这样搞又简单又好玩~

呃。就我使用单片机的经验来看,用中断是节约时间的,定时器至少比靠浪费机器周期,+1的延时函数好的多。而且貌似操作系统的进程切换机制靠的就是中断,给程序分配时间片,然后到时间切换回来,再进行判断,给其他程序分配时间,至少貌似多进程操作系统貌似...

CPU大部分时间都是在操作内存, 这里搞N个CPU, 运行任务的每个CPU除了主内存外还有一小块公共内存,用于和CPU0交换数据, 只有CPU0可以进行IO操作,比如读写磁盘操作显示之类的命令^&^(*$%^... CPU0一个作用是根据用户的IO操作,给其他CPU运行的任务输入数据,并且返回显示数据, 其他CPU不能直接操作IO, 要操作IO可以通过CPU0运行的操作系统提供的函数间接操作..

键盘之类的中断查询就OK了 不吃CPU的,磁盘操作的话直接DMA一块数据到内存里面搞定。。。对。。这个DMA控制器可以选择DMA的数据是送到CPU0的DMA内存区还是其他CPU的共享/DMA?内存区。。这个定义一下就OK 。不用CPU一个字节一个字节读 给个信号就搞定。。 这部机目前还在理论阶段 工程量比较大。

本贴中新结构的这个CPU可以随便增加位宽,还可以增加寄存器,运算器也可以增加修改成高级的。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:[s:;P]已经比较有把握搞出一套刁炸天的系统撩[s::lol] 酝酿中

呃。就我使用单片机的经验来看,用中断是节约时间的,定时器至少比靠浪费机器周期,+1的延时函数好的多。而且貌似操作系统的进程切换机制靠的就是中断,给程序分配时间片,然后到时间切换回来,再进行判断,给其他程序分配时间,至少貌似多进程操作系统貌似...

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:其实也不排除CPU0使用中断,这个精简CPU可以弄成中断堆栈版, 增加延迟和硬件开销, 这个东西两面性,

我倒是想,加入中断机制后,是否可以利用中断来实现公用RAM的数据定向传送?我YY大致是:除非下位机被中断,否则一切情况下不允许读写公用RAM,上位机写数据,向特定CPU发送中断信号,通知它读取数据,当任意下位机完成计算后,只有中断主机,然后...

找到一个平衡点,不过我想尝试一下不同以往的方法.

中断首先一个是实时性,可以在几十纳秒内进入中断处理程序回复数据,..不过有一点,装回复数据的时间

也许可以把中断响应的延迟给忽略...个人观点,处理数据传输的时候,有时中断响应时间和处理中断程序的时

间比例很大..比如中断响应消耗10ns, 进入中断后往缓冲区装数据消耗1ms,然后发数据..除非是很小的中断程序, 否则表现不出中断的实时性, 对于效率这个东西,CPU总是在执行程序

CPU转一圈回来采样一下中断信号就OK,采样一次中断信号消耗的时间和执行其他程序的时间比例也是比较大,

对于公共RAM我YY出一些机制,一般大量传输数据的话是数据流,可以开设一条DMA通道和DMA内存区不需要CPU干预,

这个方法是对付一驼一驼的数据.

CPU0要给其他CPU发送一条约定好的命令,或者是其他CPU要给CPU0发送一条命令,可以这样操作,公共RAM有TX区和RX区,

往TX区写一条命令,然后标志TX区有数据,TX区RAM数据通路切向目标CPU,这时目标CPU一看见主CPU给信号了,

马上收TX区的命令数据,然后交回TX区给主CPU,要是不交的话.....等着挨CPU0草~~~~ 拉闸%^&-_,-#.....

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 kknd:进度正在推进中[s::victory:] 最后2.5片 准备封顶[s::$]

坐等套件

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:!~ 得研究看看

突然灵感咋现!楼主知道VMP壳吗?就是把win32程序转换成一个虚拟的很简单的CPU里跑的程序,来增大代码量,我在想如果把vmp的机器码换成你小UU的指令,把小UU弄成32位的。。。啧啧啧。。。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

14片全部搞掂... 通电运行肯定够GING

软件方便.. 要是手动布估计布到明年

![指令计数器和VGA片选.png]()

![指令计数器和VGA片选_3D.png]()

![VGA时序控制.png]()

![VGA时序控制_3D.png]()

![VGA地址.png]()

![VGA地址_3D.png]()

![VGA数据.png]()

![VGA数据_3D.png]()

![SPI控制.png]()

![SPI控制_3D.png]()

![SPI数据收发.png]()

![SPI数据收发_3D.png]()

![时钟复位IO电源.png]()

![时钟复位IO电源_3D.png]()

![LED显示和手动拨码手动时钟.png]()

![LED显示和手动拨码手动时钟_3D.png]()

![LED显示和手动拨码手动时钟_3D1.png]()

软件方便.. 要是手动布估计布到明年

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 小八一3:打板打板~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~

我天天来看大神的进展

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:什么段寄存器堆栈寄存器...EAX EBX... 可以把内存单元定义为那些寄存器 然后用本CPU的指令组合..实现大部分~X86指令功能~~ 这样一看 怎么感觉X86倒像高级语言了+ + 说实在的用指令模拟X86实现X86指令功能 可能比C语言生成的代码还麻烦, X86指令集相当于高级语言了。。。里面的变址寻址相当于C语言的数组操作。。。还有CALL。。IO操作也有专门的指令 全部硬件实现[s:;P] 攻城量庞大。 堆硬件堆得够猛。 估计设计X86的攻城师刚饮左两杯二锅头 才有这个劲

哈哈。。。不过这个其实有难度,毕竟是win32下的,还是要调用api的。。。。不过也许可以直接转换机器码。。。那就爽了

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:现在想想 觉得这样搞复杂指令, 增加一个核心, 就相当于增加一个很臃肿的硬件, 功耗也大...可能内核不是功耗大的原因,, 也许是缓存? 缓存占晶体管数量也比较可观, 现在我这样搞可能没有频率优势.. 但是可以有办法增加处理单元并行处理一个任务, 比如解码播放视频, 一个CPU解,解好的二进制数据放内存或硬盘, 然后另个CPU再把解好的二进制数据读出来刷屏, 一个CPU解速度不够可以2个CPU 2个CPU不够可以3个CPU.......[s:;P] 我这个CPU现在用74搭, 目前内存还不是瓶颈, 要是内核速度比内存快就要上缓存了噢.. 不担心速度, 对影响速度的应该~运算器.

哈哈。。。不过这个其实有难度,毕竟是win32下的,还是要调用api的。。。。不过也许可以直接转换机器码。。。那就爽了

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:算了一下缓存占多少晶体管, 假设一位6个, 8位48个, 1KB 49152个, 1MB 5千万个[s::funk:] 还有地址译码逻辑??&&&&(?...

哈哈。。。不过这个其实有难度,毕竟是win32下的,还是要调用api的。。。。不过也许可以直接转换机器码。。。那就爽了

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 分立元件:那我解释一下本贴CPU执行指令的本质原理.

被大神吸引过来论坛,能讲解一下控制器原理吗?我看了“编码的奥秘”和“穿越计算机的迷雾”两本书,其它的都明白了,就是对控制器内部实现的原理不是很明白!

往常的CPU设计每种指令都有一个指令前缀码, 比如0001代表传送 0010代表运算 0011代表跳转...

但是本贴的CPU不是按照这个理念搞, 没有指令前缀码, 因为这样搞对硬件来讲很啰嗦而且也不必要...

这里的CPU传送指令,运算指令,本质都是数据传送.

下面讲一下这个CPU数据传送的控制原理本质, 非常非常的简单.

下面两张图是本贴CPU数据传送本质原理的一个简单结构模型.

图里的ROM存储器0地址装有A寄存器送B寄存器的指令,1地址装有B寄存器送A寄存器的指令,后面地址都是空操作指令.

首先复位;

复位之后给CPU第1个时钟;

第1个时钟执行之后指令寄存器锁到的是0地址的指令,会导致寄存器2锁存线拉低,并且寄存器1的数据输出到数据总线, 程序计数器加1指向1地址;

第2个时钟执行之后指令寄存器锁到的是1地址的指令,会导致寄存器2锁存线拉高锁存数据总线上的数据, 同时寄存器1锁存线拉低,并且寄存器2的数据输出到数据总线, 程序计数器加1指向2地址;

第3个时钟执行之后指令寄存器锁到的是2地址的指令,会导致寄存器1锁存线拉高锁存数据总线上的数据, 程序计数器加1指向3地址.........

指令寄存器锁到第2条指令的时候,执行第1条指令, 锁到第3条指令的时候执行第2条指令............... 工作原理真的很简单很简单..

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 nqmtlove:多谢关注... 整机电路板文件已经丢到工厂里面了 估计过几天到手.........

关注好久!快出套件!!!

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:差不多 真的很简单...

变址寻址?是间接寻址的一种吗?我这东西是不是和跳转类似?CPU结构这块我没学过。。。不过 。。貌似这玩意您给搞得巨简单。。。极端简单指令集?

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 小八一3:...测试OK先[s::victory:]

终于大板了要一套

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:好主意...

对了,要不这机子试试用铁电存储器吧!ROM/RAM合一如何?还有,其实我认为16位的也值得一搞,不过最好用贴片元件。。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:用FPGA速度吊.. 搞大机方便... 不过现在简单的电路就不麻烦FPGA了, 这样运行起来比较有"松香味"[s:;P]

还有,我个人真心建议楼主可以上FPGA了。。。。想要啥直接用语言描述仿真,方便的多。。。而且还有实用化的希望。。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:有这个意思~~![s::funk:][s::$][s::lol] 后面四个字不敢保证[s::shutup:]

不过,我在想,弄片FPGA,在上面堆个十几片32位的。。。中间弄一缓存。。。直接实用化,赶英超美

到时打算每个可能CPU里面装几个运算器, C语言里面的多元式一条指令搞定[s:;P]...也不是一条指令...要给N个寄存器装数~~~ 然后一个卡擦结果就出来~~~~搞费[s:;P]

给N个寄存器装数比较耗时间, 如果一个脉冲都装完就更加爽..因该有办法

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:多个运算器寄存器^%^*&^控制,指令位宽可能几十上百几百位, 这回好玩. 不能搞太猛 要低调[s::lol][s::L]

不过,我在想,弄片FPGA,在上面堆个十几片32位的。。。中间弄一缓存。。。直接实用化,赶英超美

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:

不过,我在想,弄片FPGA,在上面堆个十几片32位的。。。中间弄一缓存。。。直接实用化,赶英超美

某SRAM存储器的写时序.. tAS 0纳秒,,, 意思说给地址的同时可以写线拉低.. 看来内存地址都可以放在指令里面.. 这么一来内存都可以像寄存器一样操作[s::funk:]

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 小龙:估计长到月球去了[s:;P] YY一下

要是这样的话那指令要有多长啊~

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:

作为梦想未尝不可,最终和parallax公司齐头并进如何?不过,缓存分组如何?主CPU允许读写全部,但是从CPU只允许读写自己的640kb?

不纠结那个...内存不好管理/.. 有另一个结构..内存比较好管理, 缓存控制器的作用是....CPU需要的数据超出缓存的范围后CPU刹车, 然后缓存控制器再从内存取一块数据装进缓存里面, 然后CPU继续运行, 那个偏移量寄存器应该放在IO地址上面到时操作系统可以计算一个内存地址写上去然后启动任务CPU运行[s::lol] 那个偏移量加法器到底是装在上面还是装在缓存控制器里面... 装上面会增加CPU和缓存的地址延迟, 装下面应该好点..

缓存1MB, 要是有个蛋疼的人写个2MB的顺序程序 估计CPU会被气吐血....

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:YES!!! 差不多是这个意思, 输入时钟极限周期和这些器件延迟总和有关(累加器延迟+加法器延迟+比较器延迟+两个门的延迟).

俺的想法是这样的哈,一个时钟过三态门,累加器+1,累加器数据和锁存的地址数据相加,累加器的地址就送给缓存的地址线,缓存的数据线通过三态门和内存数据线相连,缓存的读写使能线拉高,写,内存的拉低,读。加法器送出来的地址一边进内存,一边进同或门,...

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 大胆哥:马上又要吹个牛逼

又上来看楼主吹牛逼了

。。

。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:。。。话说。。似乎又想到有个新结构可以让CPU大部分时间全频工作不受内存延迟影响,不使用缓存,如果搞成功的话。。 该不该公开。。。@大胆哥

俺的想法是这样的哈,一个时钟过三态门,累加器+1,累加器数据和锁存的地址数据相加,累加器的地址就送给缓存的地址线,缓存的数据线通过三态门和内存数据线相连,缓存的读写使能线拉高,写,内存的拉低,读。加法器送出来的地址一边进内存,一边进同或门,...

好像不管怎样CPU速度都要受制内存/缓存[s::L]

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 虎哥:老虎建议很不错~~~!。要是搞出来 这个新结构名称可能是《KC-LS分散内存阵列变频执行结构》 名称很N的样子 看名称应该就知道大概。[s::lol] 这个结构即使使用100ns(10MHZ)的指令存储器,CPU的速度也不会受制于存储器,用高速门电路搭跑上百M~~~[s::lol]

应该早公开,但有公开的技巧。

1、要清楚新结构在业内的水平,看看前人有没有做过类似的或相同的。

2、要给新结构取个容易记住的名字,比如龙少结构。

3、公布以后要加以宣传,最好是平面媒体。每次楼主发的结构,KC都用微博等渠道推过。但是如...

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

用100ns的指令存储器, 按理CPU是跑10MHZ内, 怎么可能跑到100MHZ(单周期)[s::funk:]~~~ 到时变个魔术给你们看怎么实现

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

- - 20号下单今天才到手.... 打样14种 一打开发现刚有8种, 问老板 答复是补料延迟了...剩下6种今天早上已经发货....0_+#~!~!

![QQ图片20141230010756.png]()

![DSCF2957_调整大小.jpg]()

![DSCF2958_调整大小.jpg]()

![DSCF2959_调整大小.jpg]()

![DSCF2960_调整大小.jpg]()

![DSCF2961_调整大小.jpg]()

![DSCF2962_调整大小.jpg]()

![DSCF2964_调整大小.jpg]()

![DSCF2965_调整大小.jpg]()

![DSCF2966_调整大小.jpg]()

![DSCF2968_调整大小.jpg]()

![DSCF2970_调整大小.jpg]()

![DSCF2971_调整大小.jpg]()

![DSCF2973_调整大小.jpg]()

![DSCF2974_调整大小.jpg]()

![DSCF2977_调整大小.jpg]()

![DSCF2978_调整大小.jpg]()

![DSCF2981_调整大小.jpg]()

![DSCF2983_调整大小.jpg]()

![DSCF2984_调整大小.jpg]()

![DSCF2987_调整大小.jpg]()

![DSCF2988_调整大小.jpg]()

![DSCF2990_调整大小.jpg]()

![DSCF2991_调整大小.jpg]()

![DSCF2993_调整大小.jpg]()

![DSCF2995_调整大小.jpg]()

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:[s::lol] 理论阶段~ 硬件延迟高的指令低频 ,硬件延迟低的指令高频, ~ 内存分散成多组, 不连续对同一组操作就可以提高速度... N通道. 要是连续对同一组操作就降频.. 好像这样搞又很麻烦

我猜猜。。。变频执行靠除法器实现?给不同的设备不同的时钟,但是同步怎么办?

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 表慌张:不算先进~ 玩具水平, 多任务需要中断的系统可能上不了 [s::lol] DOS差不多的就可以上

先进,,,不明觉厉 国产有个打酱油操作系统 移植过来呗。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 rpg-7:应该不用这么复杂...CPU的话..存取数这个地方设计得高速一点也容易, 整浮四则运算器也容易搞, 觉得主要是要研究出个高效的存储器结构.

顺便@虎哥,我个人认为可以搞个KC软核的项目页面了。。。。大家把资料放上去,集思广益 。。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 csaaa:如果一定要中断马上执行紧急程序那就安排其中一个CPU专门监听中断信号.. 中断信号一到可以在ns/ps级别的时间内启动中断处理CPU执行中断程序, 定时器/计数器属于外设, 可以放在IO上面, 本贴的套件机有一个指令/脉冲计数器, 可以当作定时器来用, 也可以用来计算程序的CPU占用率...

楼主把中断和定时器也做进去,下一步把多CPU的协调工作也做进去,再下一步把内存和高速缓存给区分开来并设计一些内建的指令集要求兼容51内核的。思路出来后我们保持联系哦,

个人觉得什么指令集已经不重要~ 重要的是这套指令是否能组合实现全部算法/程序/C编译器, 我目前CPU设计理念是找到指令和硬件的一个平衡点, 既能搞出需要指令, 也不把硬件搞臃肿, 否则搞出一条臃肿指令缩减执行时间,但造成主频下降,还不如不做这条指令, 用其他指令组合实现, 两边一扯性能差不多,而且还不用把硬件堆臃肿.

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 kknd:准备可以开机 正在焊 边焊边叹[s:42]

套件有希望了。。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

PCB已经全部到, 目前焊了一半, 眼花= =, 图里面的接口插针还没全部插进去(摆拍).

![DSCF3069_调整大小.jpg]()

![DSCF3070_调整大小.jpg]()

![DSCF3046_调整大小.jpg]()

![DSCF3048_调整大小.jpg]()

![DSCF3053_调整大小.jpg]()

![DSCF3054_调整大小.jpg]()

![DSCF3056_调整大小.jpg]()

![DSCF3057_调整大小.jpg]()

![DSCF3058_调整大小.jpg]()

![DSCF3059_调整大小.jpg]()

![DSCF3060_调整大小.jpg]()

![DSCF3068_调整大小.jpg]()

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 liangjiajing:永和村= =~

楼主是南宁的?南宁哪里啊

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

全部焊完,,,,,,,,OK改天插IC上去开机~ 希望不爆炸[s::funk:]

![DSCF3085_调整大小.jpg]()

![DSCF3107_调整大小.jpg]()

![DSCF3108_调整大小.jpg]()

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 zhu1982lin:期待你的好消息...

粗略看了LZ的CPU(没仔细分析),想起当年我用VHDL在FPGA上修改别人的代码,完成了一个简单的PIC单片机.

真没有想到简单的MCU能用三十多个IC就能完成了.

而且我现在都不知道怎么把信号转成VGA方式,输出出来, 当时,我是用一个...

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 nierbia:准备21~~~老了[s::Q]

看到这个帖子,我特意申请了一个账号过来顶你。你多大年纪了?居然有这般功力。楼主,可以透露一下年龄吗?

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

正在测试中, 在手动拨码测试... SPI工作正常, VGA工作正常, 顶板LED要重新打过一次... A寄存器和B寄存器两组LED反了= =...

实际看起来要劲得多..

图中机的套件 附带一个电源, 定价339.1¥。。。。额好吧表示抽了点油水- -。。。不然不用吃饭了。。

![DSCF3121_调整大小.jpg]()

![DSCF3124_调整大小.jpg]()

![DSCF3125_调整大小.jpg]()

![DSCF3127_调整大小.jpg]()

![DSCF3130_调整大小.jpg]()

![DSCF3132_调整大小.jpg]()

![DSCF3133_调整大小.jpg]()

![DSCF3134_调整大小.jpg]()

实际看起来要劲得多..

图中机的套件 附带一个电源, 定价339.1¥。。。。额好吧表示抽了点油水- -。。。不然不用吃饭了。。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 kknd:...............出现了一个BUG......时间差了几纳秒[s::funk:].........要修改一片PCB增加一两片244 + +~~~~ 下个星期才有结果了............[s::Q][s::L]

怎么拍?PM链接。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

CPU出现了两个BUG- -... 一个是74XX181的"A=B"输出信号居然是开漏输出[s::funk:] 仿真又通过..奇怪... 必须要搭上拉....现在飞接电阻解决(之前很有把握所以偷懒了没有仔细测试- - , 这个"A=B"信号是第一次用), 另一个是数据传送时序BUG...数据提前消失了写信号才到......[s::L] 导致某些操作后面必须附加一条指令让数据保持...

上面两个BUG要修正两片PCB... 估计下个星期PCB才到...

现在在8MHZ的频率下运行了一个读内存卡数据显示的小程序, 手工二进制编程... 成功运行.. 等下刷图看看效果怎样[s::lol]

![DSCF3137_调整大小.jpg]()

![DSCF3143_调整大小.jpg]()

![DSCF3150_调整大小.jpg]()

![程序2.png]()

上面两个BUG要修正两片PCB... 估计下个星期PCB才到...

现在在8MHZ的频率下运行了一个读内存卡数据显示的小程序, 手工二进制编程... 成功运行.. 等下刷图看看效果怎样[s::lol]

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用 nmasdf:我尽量搞快点###[s::handshake]

求购一套,太酷了!!!

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

刚才把SPI的速率调到13.5Mbps,SPI是独立时钟, 换算过来读内存卡速度上MB/S了.. 无压力... CPU 12MHZ可以跑, 13.5Mbps的速率传送数据等待SPI的空操作可以删除, 目前分辨率256x240,刷图13帧/S[s::lol] 高级点的程序等弄了这个CPU的专用编译器再搞, 计划是开机ROM里面的启动程序是固定的, 启动程序的基本功能就是开机搜索XXXXXXN文件并载入装载运行ROM, 然后运行, 在装载运行ROM上面运行的程序如果要启动其他程序的话还可以通过RAM传递一个文件起始簇号或路径文件名给开机运行ROM, 然后切换运行开机ROM, 这时开机ROM就会根据约定好的的命令还有簇号,执行操作 恩差不多就这个意思.

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

测量了整机工作电流, 5V情况下. 1安左右.

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。