有分段滤波,带驻波测试功能的频谱?

优先检查电路板匹配,一般是因为器件外的电路有较大反射导致的。

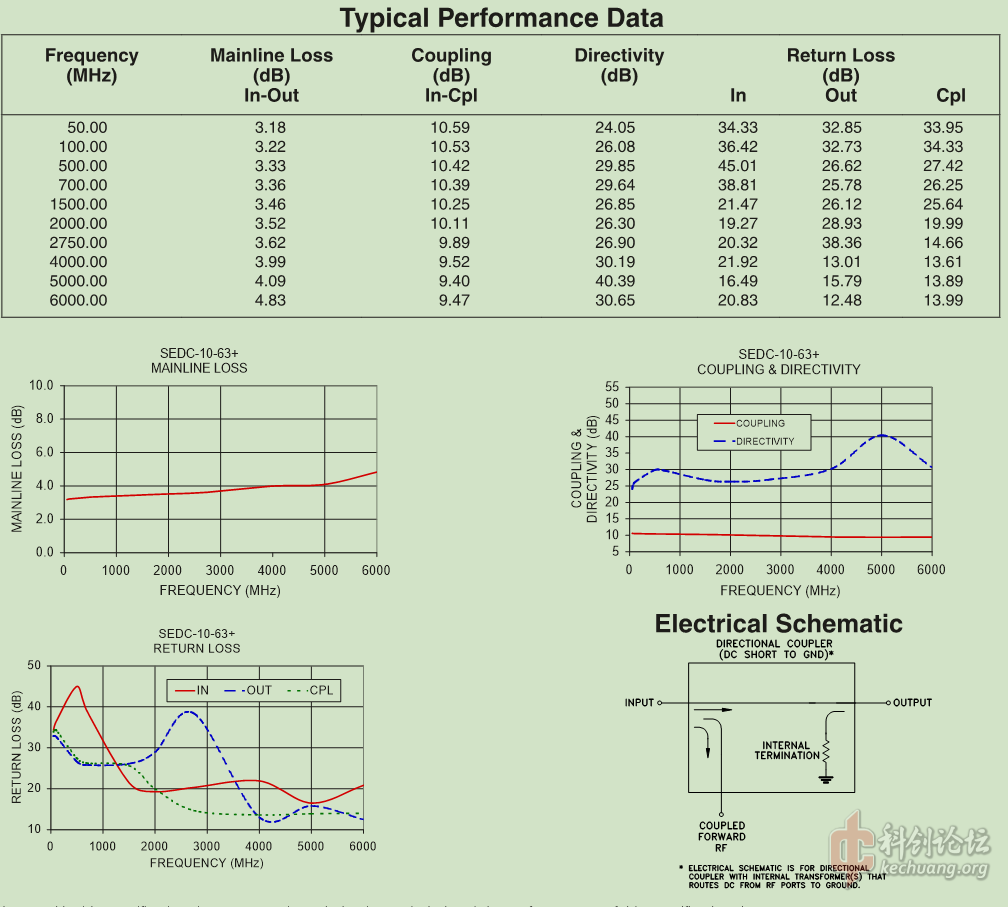

SEDC-10-63应该是一个带内部匹配的非等臂惠斯登电桥,性能良好。

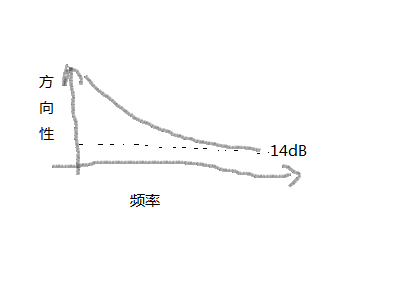

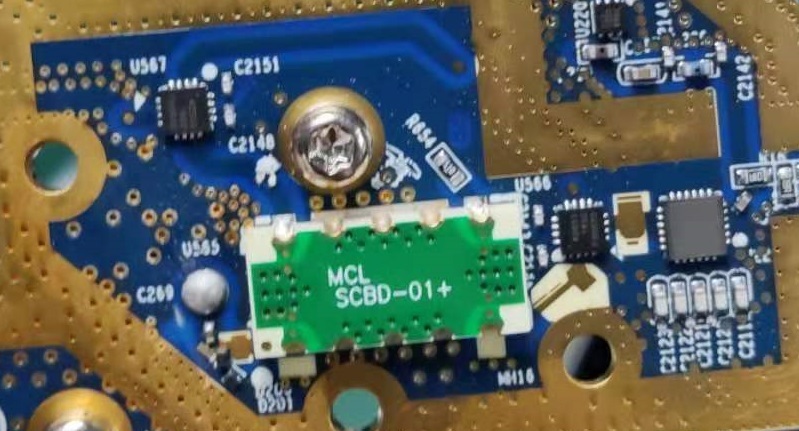

图1

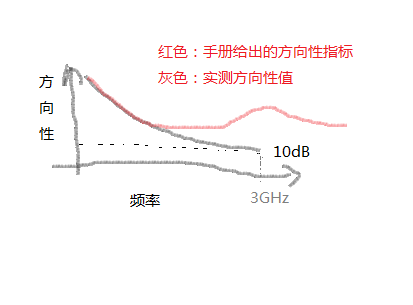

图2

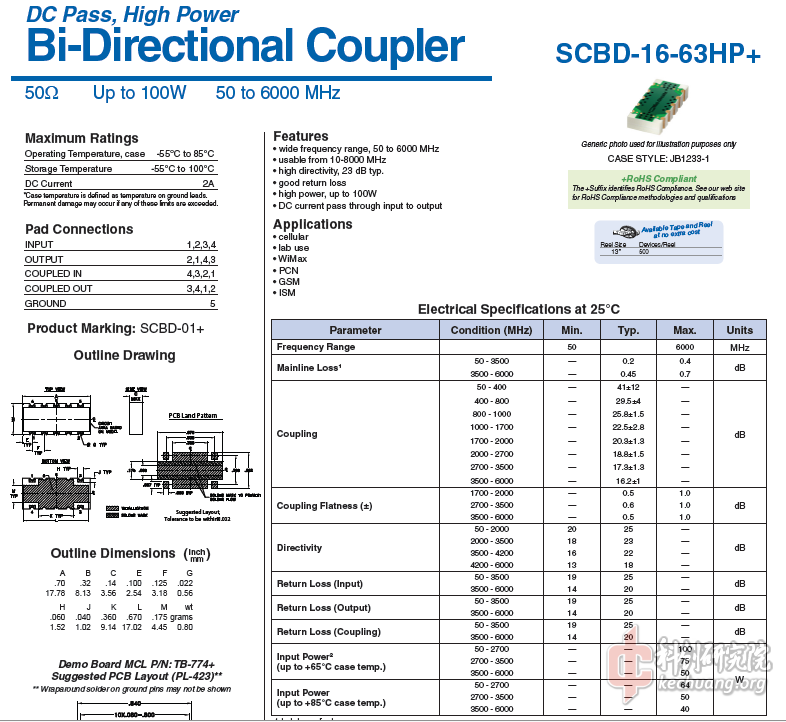

图3

图4

各位大神好,我想请教下我使用的MINI circuit公司的驻波电桥SEDC-10-63,其方向性与手册出入为何如此之大?

实验过程:

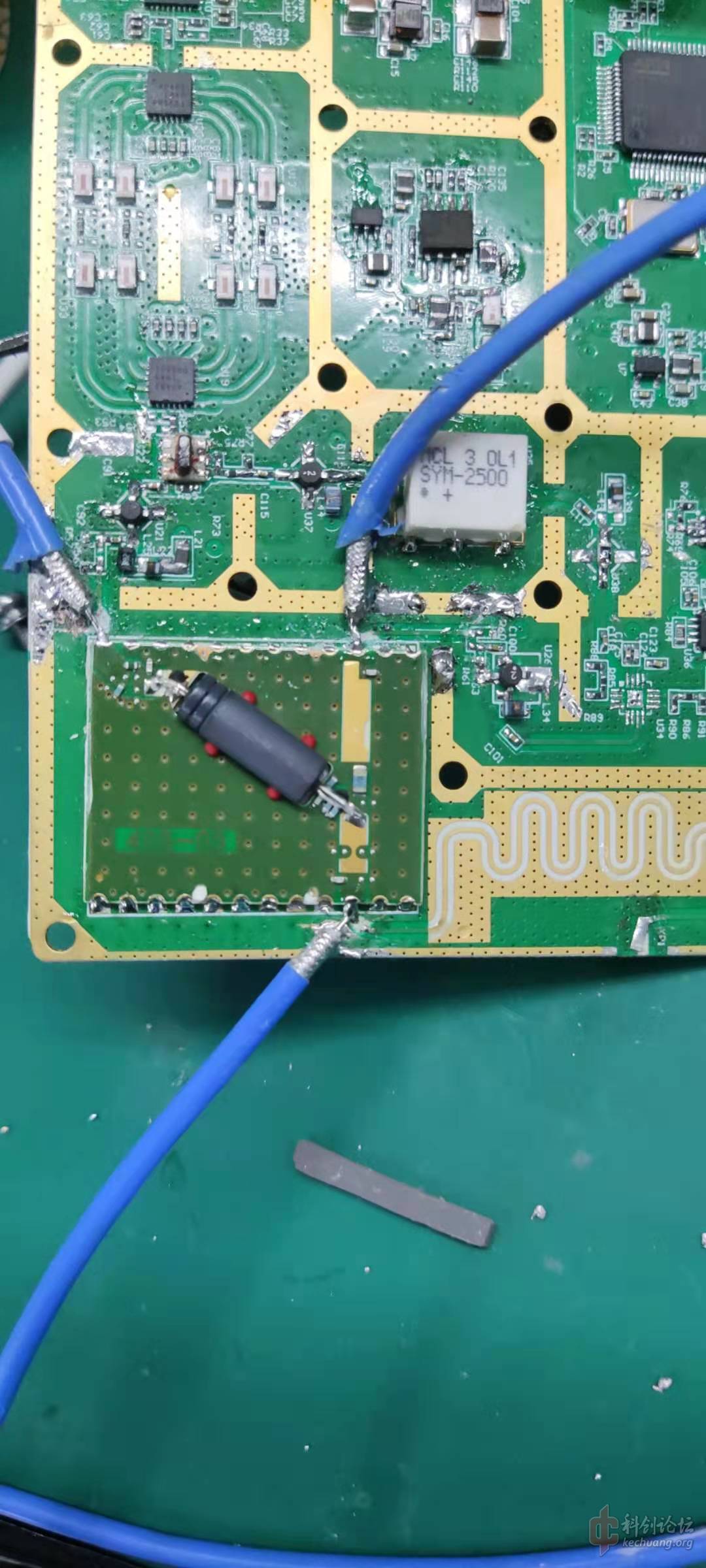

将3根射频开路线分别焊在芯片的3个端口上

output端口输入是德信号源扫频信号,coupled端口接是德频谱仪

input通过接开路校准件,50欧姆负载校准件来测量电桥方向性

图2,图3两块电路板的测试结果基本相同

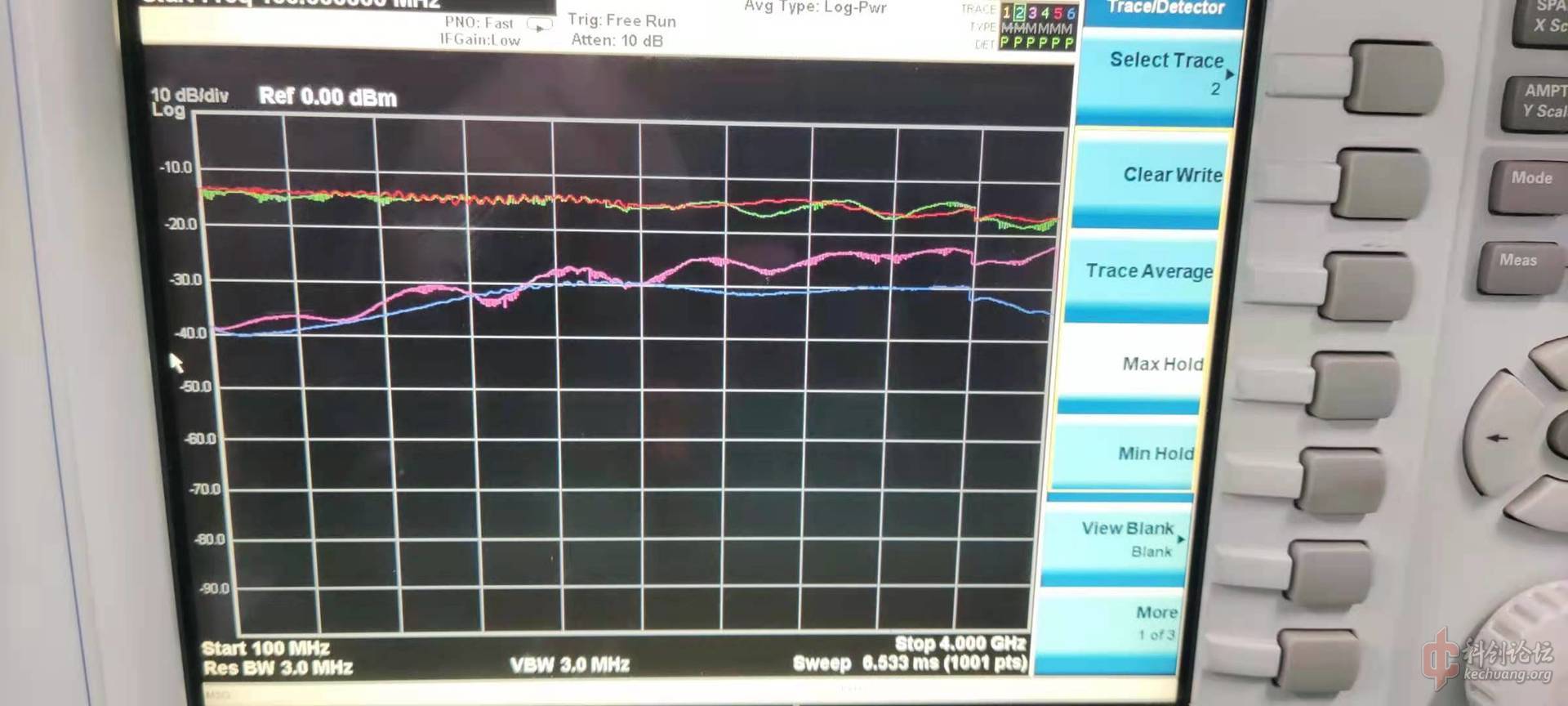

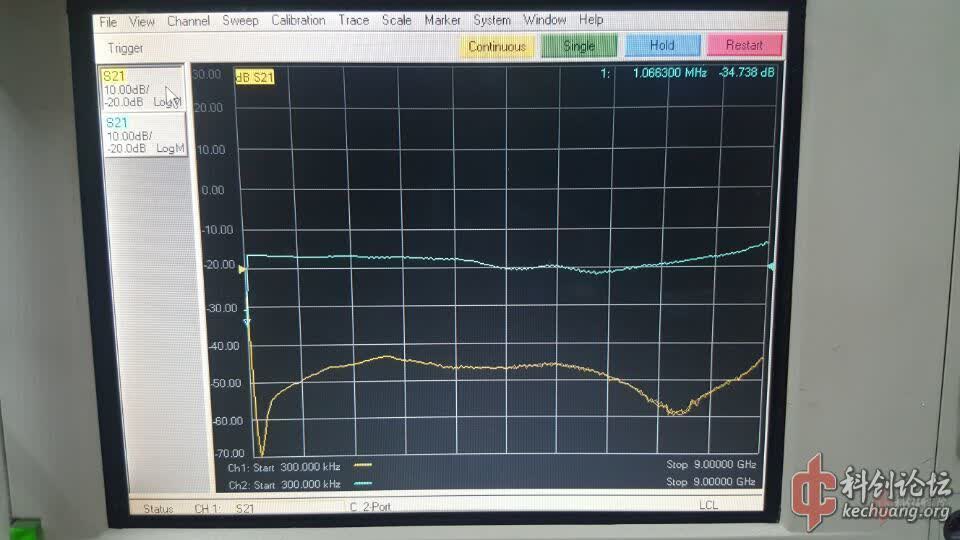

图4中

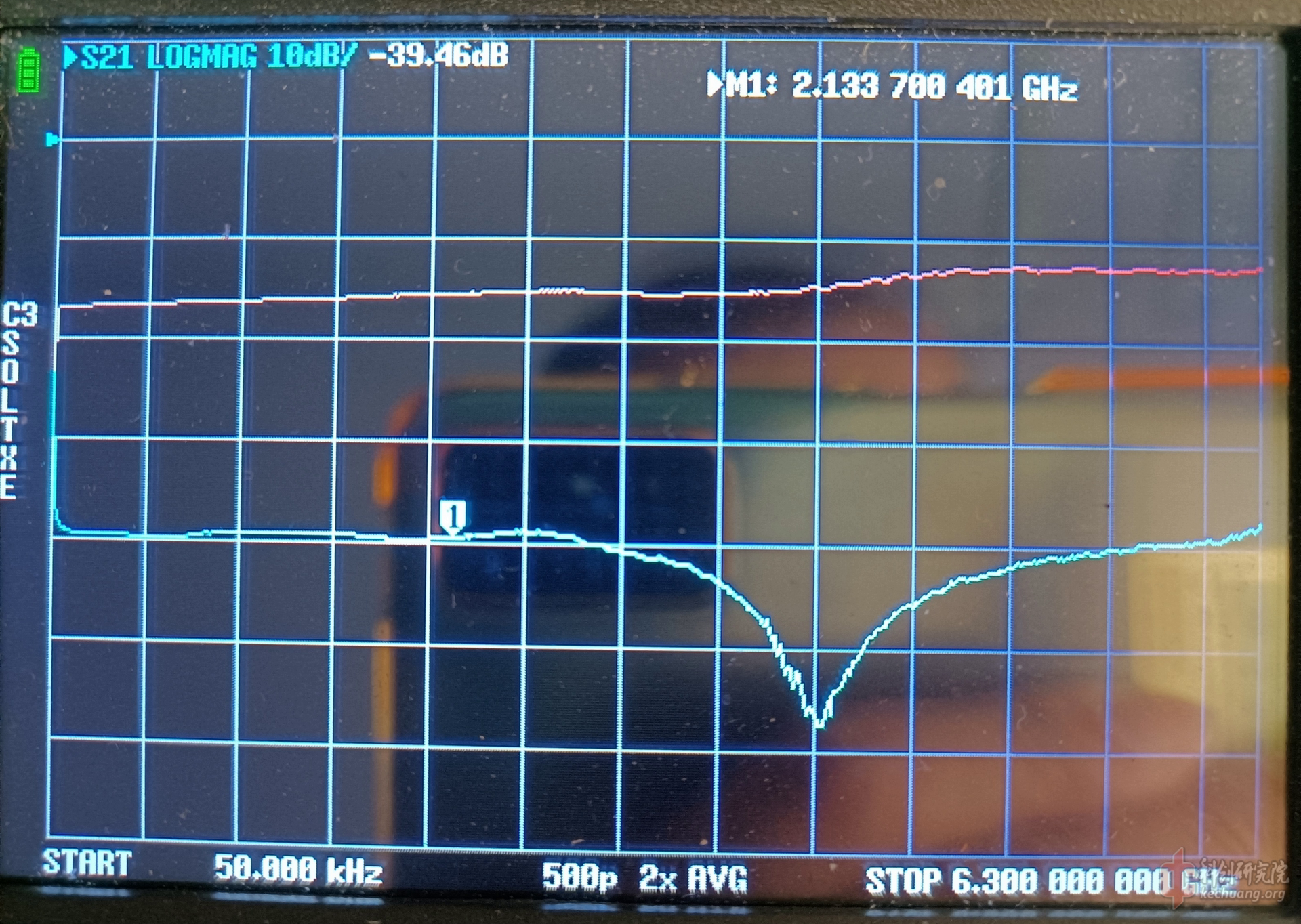

电路板的测试结果是:绿色的谱线是接开路校准件的测试结果,粉红色的谱线是接50欧姆校准件的测试结果

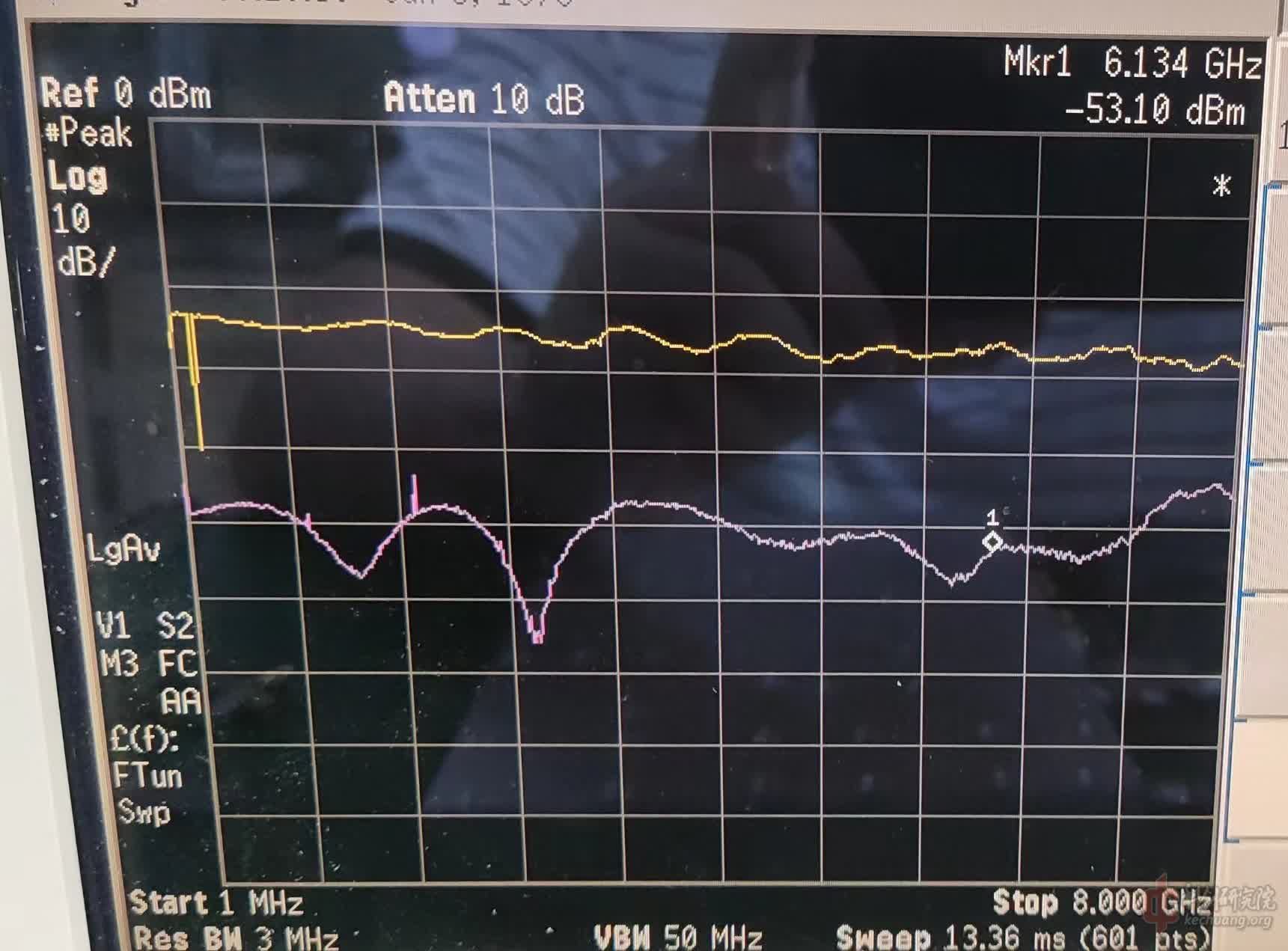

我单独做实验将驻波电桥芯片放在屏蔽盒里(很小的屏蔽盒,只能放下一个驻波电桥及其实验的pcb板,电桥与屏蔽盒上的3个N型连接器进行连接)(未拍图)

基于屏蔽盒的测试结果:图4中 深红色的谱线是接开路校准件的测试结果,浅蓝色的谱线是接50欧姆校准件的测试结果

注:发现屏蔽盒的上盖板不影响测试指标,在屏蔽盒里加吸波材料也不影响测试指标

我将图2,图3的电路板放入大屏蔽盒里,测试效果还要再差一些,如图5,黄线的读值即为50欧姆校准件与开路校准件测量结果的差值

图5

疑问:

官方手册驻波电桥方向性至少有25dB;

1.为何单独给驻波电桥做实验放在专门设计的小屏蔽盒里指标要好一些,但仍没有达到官方手册的指标?

2.为何在系统PCB上设计的电路驻波电桥方向性如此之差?(用射频开路线焊接测量)

3.为何在系统PCB上设计的电路驻波电桥加盖上大屏蔽盒后方向性变得更差了些?(图5的黄线)

有分段滤波,带驻波测试功能的频谱?

优先检查电路板匹配,一般是因为器件外的电路有较大反射导致的。

SEDC-10-63应该是一个带内部匹配的非等臂惠斯登电桥,性能良好。

几个端口的失配是可能造成一定的性能下降的。我看了手册,他们使用的是共面波导,你用的是带状线,我怀疑可能是过渡的接口处理的不太好。我没有这种模块的调试经验,只是提供一个建议,希望后面能看见你的反馈。至于那个盖子,可能是它的边缘起了作用,调节了不匹配,这是我的猜测。还有,你的焊接不太好,中间的线留太长。

不用怀疑MINI的数据手册。

刚看了一下,DUT端焊了根线,再接50欧标准负载测耦合器的方向性!!

把线都测进去了。难怪不准

抱歉工作有点忙,测试时附近的微带线我都割断了,再焊接射频开路线测试的。甚至我把画的微带线全割了,3根射频开路线都直接焊在器件的焊盘上,指标曲线也是一样的差(曲线重合),波浪式恶化。

我在OUTPUT,COUPLED各接5dBπ型衰减器实验发现对方向性均没有改善。

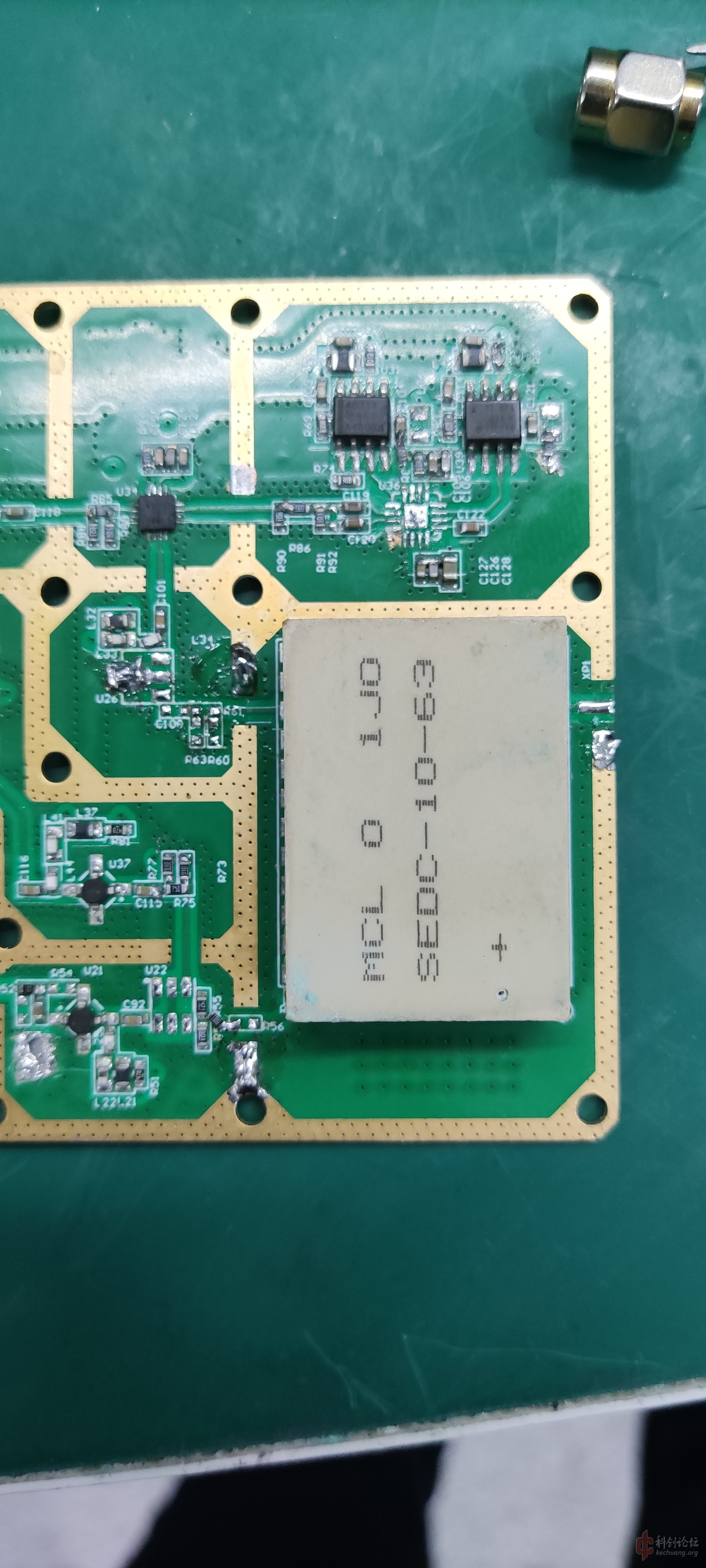

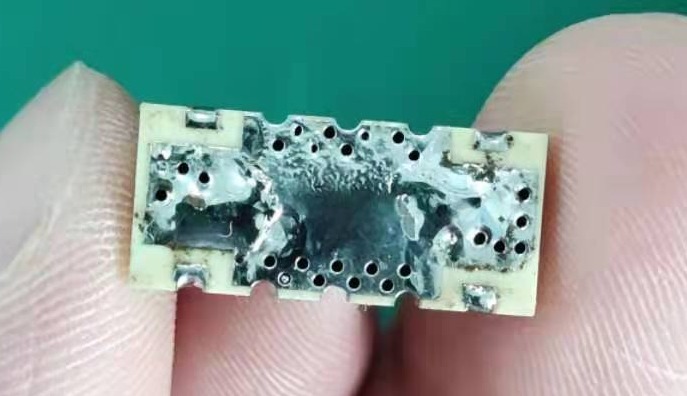

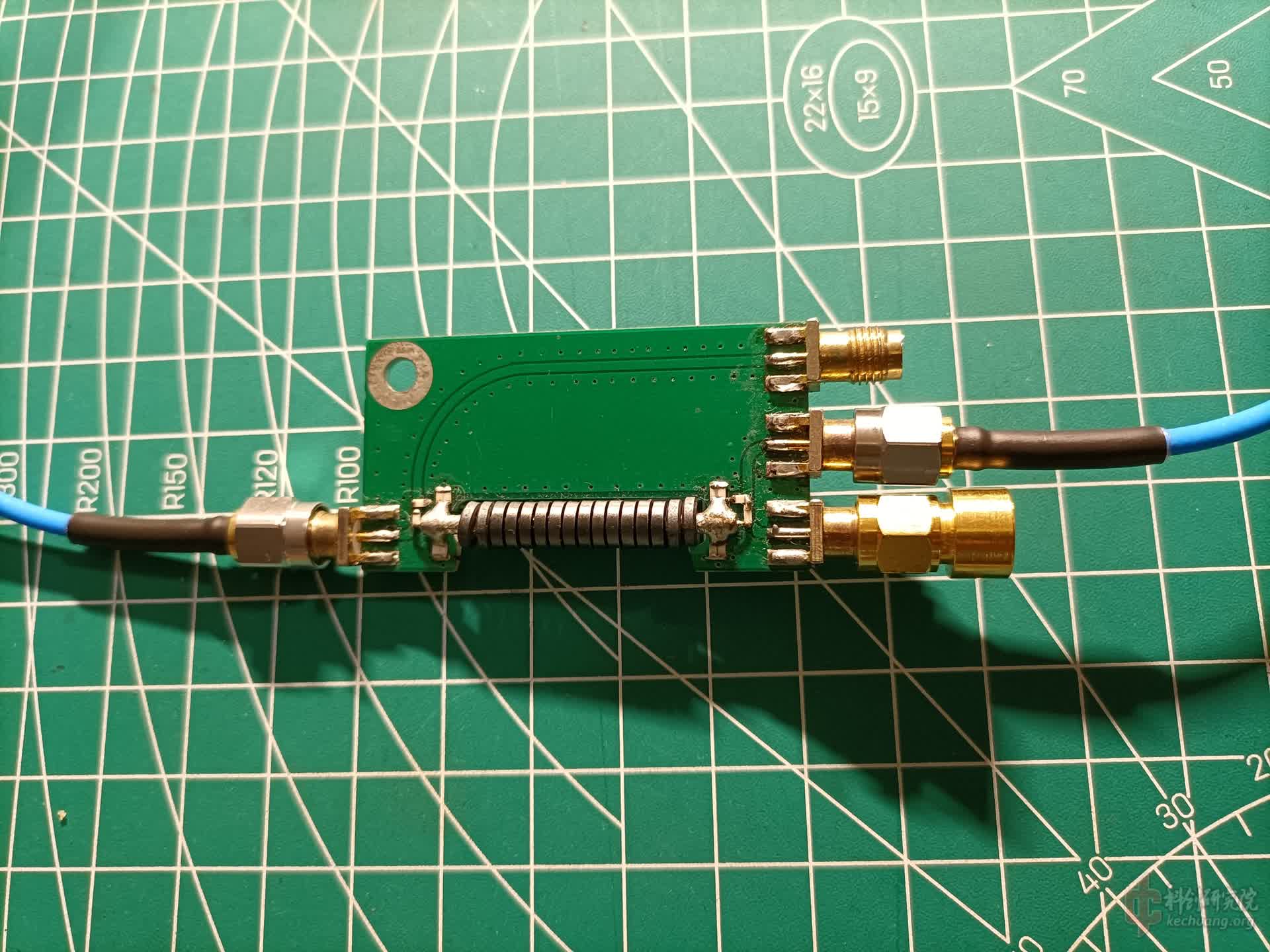

上图即放在小屏蔽盒里用于专门测该器件指标的。

指标即如下:

图4中 深红色的谱线是接开路校准件的测试结果,浅蓝色的谱线是接50欧姆校准件的测试结果

注:发现屏蔽盒的上盖板不影响测试指标,在屏蔽盒里加吸波材料也不影响测试指标

哎:发现驻波电桥自己设计的实际做真难,找资料(都是4GHz以上的设计资料)换了各种设计方案指标高频做到1-2GHz还凑活,再高就不行了。目前发现坏的3GHz安捷伦失网里的驻波电桥指标自己实测确实很好,但根据它那电桥专利自己做的驻波电桥指标就只到1GHz多一点了。太难了。

虽然小屏蔽盒的实验板与官方画的有区别

不过如上图画红圈 处,官方给的RO4350B板材的介电常数为2.5,厚度为5.588mm,应该不对吧?

处,官方给的RO4350B板材的介电常数为2.5,厚度为5.588mm,应该不对吧?

2.5与RO5880的介电常数接近。RO4350一般按3.66设计或遵从制造厂意见(比如3.48)。

看见波浪几乎肯定驻波大,至于何处驻波有多大,可用矢网时域变换辅助查找。

降驻波的方法需要从传输线原理上找,建议复习后灵活运用。

普通贴片电阻焊接的π形衰减器匹配不佳,但4G应该没什么问题。若有较高要求,可买mini的成品。

焊接技术要提高,锡多点少点效果都不一样的。

谢谢虎哥提示,不过4G确实做不到,我试试看失网的时域图分析下。试试在小屏蔽盒上用电感电容进行端口驻波匹配,我测了小屏蔽盒的端口回损低端有-35dB附近,高端回损只有-13dB~-18dB,确实不怎么好。

还不是很明白LZ是怎么测耦合器的,

耦合器INPUT端的走线、N头、N头负载能确保S11优于30DB吗?

电桥的OUTPUT端和耦合端,建议接个S11比较号的15DB衰减器,再测试一下。

可以尝试重新画个pcb用高质量sma头焊好,这种N头如果不好好处理S11基本干不下-25的

对近期工作的总结:

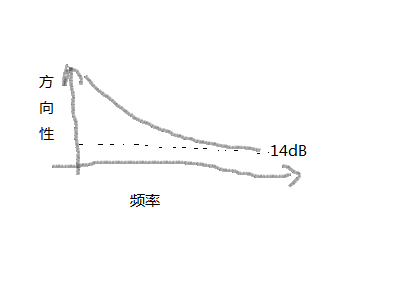

1、后面我又重新制版,做成双面板,而不是以前的四层板,现在该器件3.6GHz方向性指标已达到14dB,而且方向性曲线是平滑过渡,单调下降到14dB,整体效果有明显改善,效果如下图。不过与器件手册方向性指标25~40dB,仍差距明显。此次改善增加了大量接地孔,不是是否是主要原因。

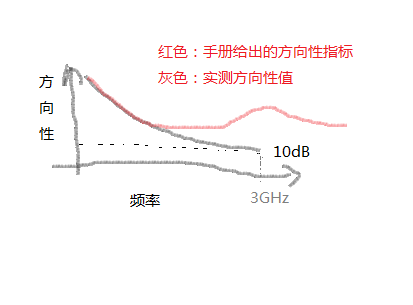

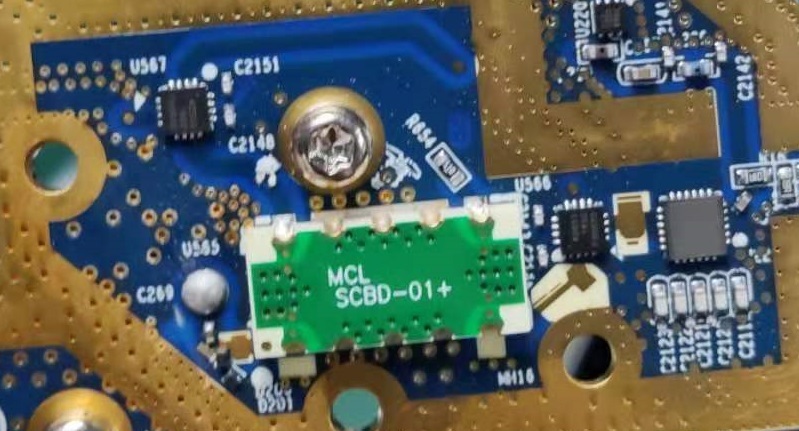

2、同期我又换了一个定向耦合器SCBD-16-63HP+做实验,手册上方向性指标至少有20dB,但我实际测试效果在3GHz时只有10dB了,不过在1.5GHz及其之前频率,与手册指标基本吻合。

我看到相关视频资料别人也用过该器件,不过别人在它的输入输出口用微带电路进行了端口阻抗匹配(耦合端和隔离端并没有进行匹配,右下角输入口连接的是步进衰减器和开关,左下角输出口连接的是N型头,信号是从右向左流动),我用mini-circuit官方的S参数文件进行仿真,仿真结果和手册给出的指标一致,并不需要匹配啊,不知他人进行匹配的技巧是什么!

我想最难的就是匹配方法了。

唉,用纯PCB打评估板,SMA水平连接器引出,不要装壳子。您那个壳子里面PCB螺钉距离连接器那么远,整个就是一电抗器。我在上面已经提示了要从传输线原理上找原因,做东西一定要动脑筋想他的道理,每一个环节弄明白,不费脑子就会费体力费时间,有的时候真的是十年工作经验不如一年爱动脑子。

唉,用纯PCB打评估板,SMA水平连接器引出,不要装壳子。您那个壳子里面PCB螺钉距离连接器那么远,...

虎哥,这么晚还回复我的问题,辛苦了

后面做的PCB使用的大的定向耦合器SEDC-10-63就是用纯PCB,双面板,如下图,用的SMA连接器(通过4个螺钉安装到屏蔽盒上那种SMA(正品非淘宝货),没有直插/螺钉压到板子上的那种连接器,那个太贵了,一个就要好几百块钱)做的测试效果。(部分PCB螺钉距离确实连接器那么远,微带线不是直的是因为如果测试没问题,PCB板就可以直接使用,连接到电路当中,不需要重新更改了)

小的定向耦合器SCBD-16-63HP+还没有做PCB板,是用2根1分米长的SMA开路测试线焊接在器件上,输出端焊盘直接焊接/不焊接49.9欧姆来实现开路和接负载的状态,来测出下面的测试数据(这个的测试确实不严谨)

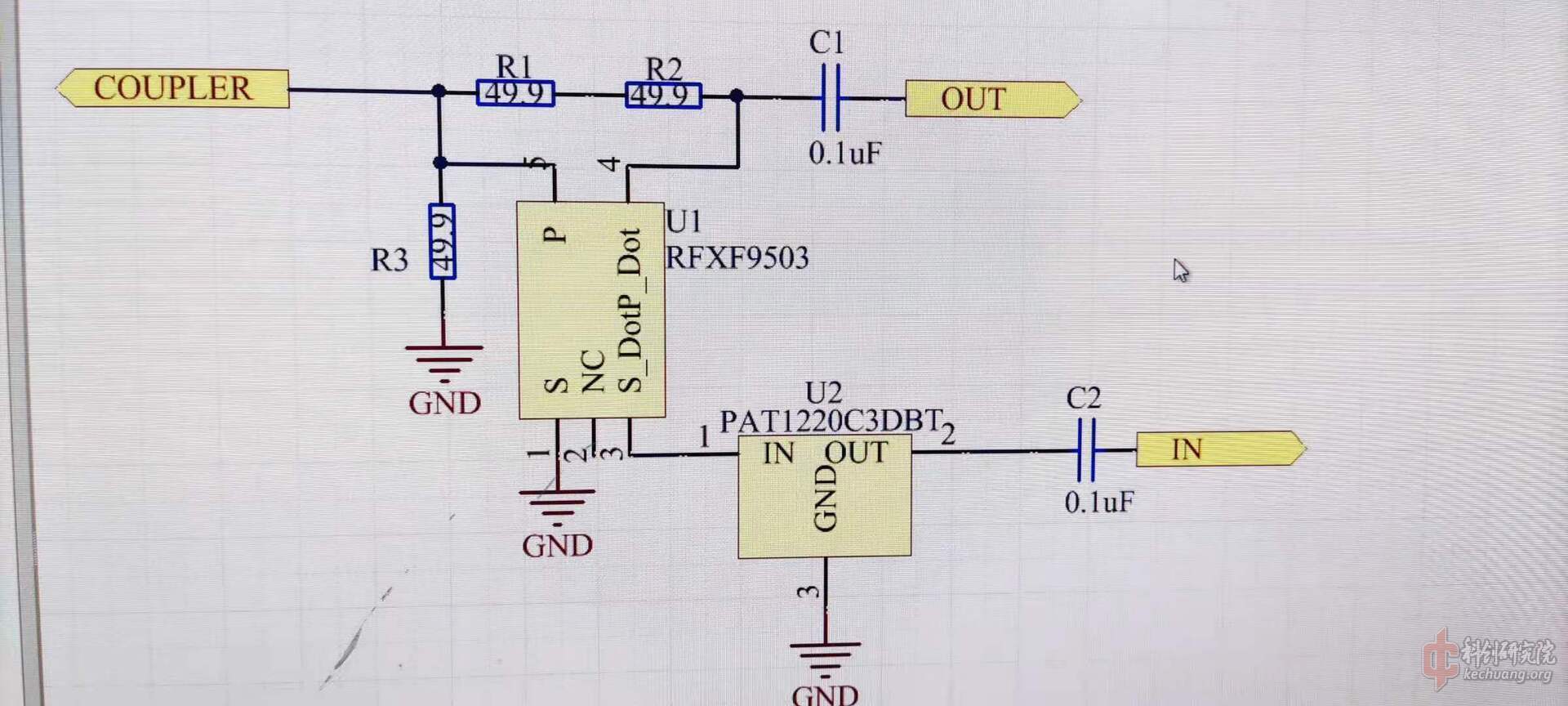

今天我网上看到miniVNA的资料,用它的电路进行了测试如下图,在2GHz以内方向性能达到20dB及其以上,2GHz-3GHz指标就逐渐恶化了,看了下巴伦RFXF9503手册只工作到3GHz,2~3GHz的S11只有7dB左右,

下次计划选用MABA-011082(5MHz~8000MHz)的巴伦做下实验,看看方向性是否能改善了。

虎哥,就算单独模块做的好,做在电路里肯定也会恶化啊,我希望的做到下图中的效果:器件在电路中,指标还要好,就是不知道下图中的设计匹配是依据什么来进行匹配的(看匹配的微带结构还挺复杂的)(当然这块板子的方向性指标怎么样,我也不知道,应该很高吧)

今天我换了3种1:1的巴伦在如上pcb上做实验,

测试效果如下:

1MHz~3GHz巴伦:1GHz以下方向性平均能到30dB,2GHz时方向性只有15dB了,3GHz时方向性只有4dB了,方向性曲线比较剧烈。

10MHz~6GHz巴伦:3GHz以下方向性平均有12dB,2Ghz附近还恶化到只有10dB。3GHz以下内整体方向性较差,但方向性曲线比较平滑,带内变化不大。不像上一个1MHz~3GHz巴伦1GHz以下方向性特别好有30dB方向性。

5MHz~8GHz巴伦:特性和10MHz~6GHz巴伦相似,但整体指标要好5dB左右。3GHz处能做到17dB方向性,500MHz处只有14dB方向性。1GHz以下方向性指标远不如1MHz~3GHz巴伦。

后面有时间再做实验。

考虑把焊点处理一下?不清楚你现在这种毛刺或者多锡能有多大影响 不过频率越高影响越大是肯定的

上接16楼的评论。

在测试过程中有几个细节:

1.将其中一个SMA接头(用来接SMA50欧姆标准负载)替换为50欧姆贴片电阻,并没有任何改善(变化)。

2.一开始器件上并没有多少锡,后面怕因为是锡少的原因进行了加锡,测试发现加锡前后并没有改善(变化)。

由于SMA接头离元器件之间留有缝隙,下次有时间重新处理下后,再做次实验。

我把缝隙给去掉了,基本和手册指标相符(剩下的差异应该是不太好的50欧姆负载带来的,用好的负载应该结果基本一致)

下图两条曲线的差值即为方向性。

我把缝隙给去掉了,基本和手册指标相符(剩下的差异应该是不太好的50欧姆负载带来的,用好的负载应该结果...

另外把PCB覆铜铺到板边,别留间隔,不然会增大SMA到PCB的连接处阻抗不连续,特别是高频

由于整合到pcb上时指标急剧恶化而不能使用,只能做成模块,算是半个解决了吧。

参考的是homevna的电桥方案

实测效果图,9khz时还有6.5dB的方向性,10GHz带宽内基本和原作者的做的指标一致

上图是科创的效果图,离科创还有很大差距呀。

引用wzh19940105发表于19楼的内容另外把PCB覆铜铺到板边,别留间隔,不然会增大SMA到PCB的连接处阻抗不连续,特别是高频

最近又试了一下,发现把SMA接头换成开路同轴电缆焊上去就行了,SMA头附近的阻抗真的很难弄,做了好几次板子了,效果都不想,昨天发现bird公司的电桥的实现方法竟然想法和我一致,缺点是体积大,占面积,不过bird公司的矢网有空间。

由于整合到pcb上时指标急剧恶化而不能使用,只能做成模块,算是半个解决了吧。参考的是homevna的...

低频没下去,说明桥未平衡,电阻值还可以改。不过低频平衡了可能高频又变差了。

说实话现在这种磁环桥已经淘汰了,大概是因为磁性材料有少许幅度相关的非线性,折腾的必要不大。

不知怎么看到了这个帖子。请问楼主的问题解决了吗?

如果电桥定向性不好,那么优先检查DUT端口的阻抗连续性。大概率是在电桥到电缆的连接界面有大反射。电缆一般不太差的话,电缆本身和电缆的SMA工头的阻抗都还行。你焊电缆的地方可能芯线剥多了;电缆的地皮只焊到了共面波导的一侧地而不是两侧地,这都会导致在焊接处有个阻抗抬高。

楼主用的这种电桥我2017年时做过,我做了个“创新”,一个巴伦左右各带一个桥,同时把两个方向都测了。这几天想回顾一下过去的工作,翻出来测了一下,还不错。低频本来定向性可以更好的,我电阻没有用太精确的。否则低频定向性应该可以提高到30甚至40dB以上。不过低频本来就可以通过软件提高定向性,折腾的意义不是太大。

| 时段 | 个数 |

|---|---|

| {{f.startingTime}}点 - {{f.endTime}}点 | {{f.fileCount}} |

200字以内,仅用于支线交流,主线讨论请采用回复功能。