本帖最后由 神之觉醒 于 2013-10-15 22:49 编辑

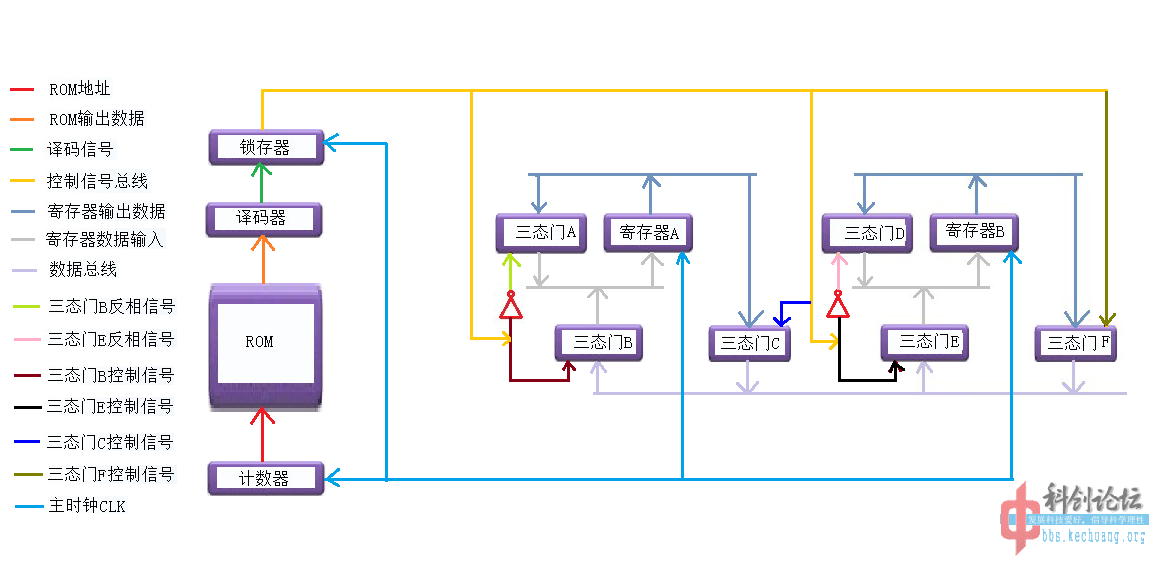

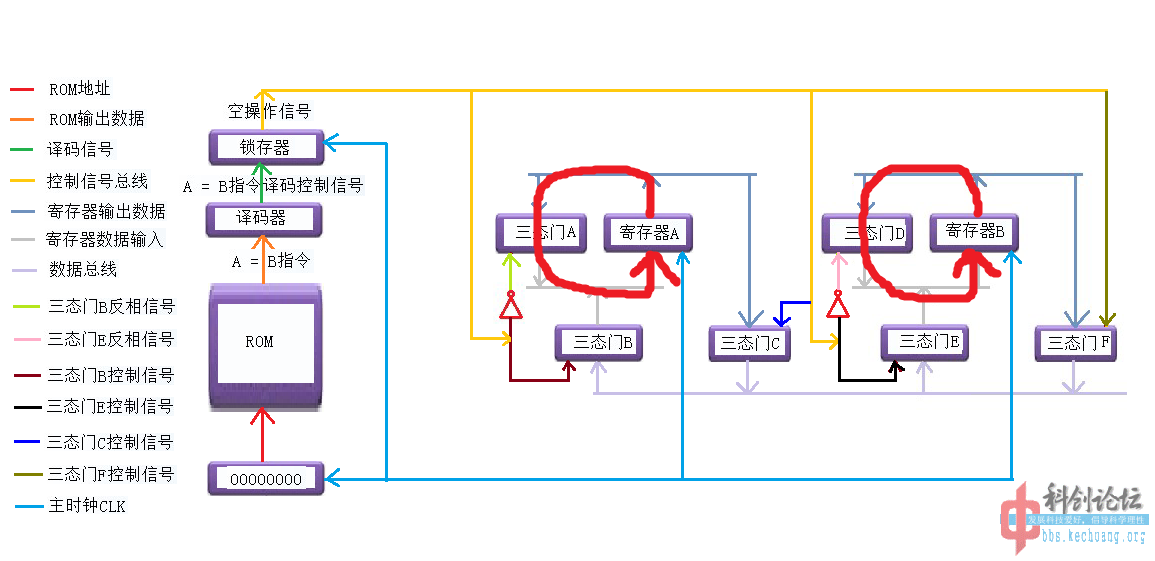

类似2级流水线效果图:

![时序.png]()

取指令和译码步奏合为一体,就是取控制信号,然后就是锁存,锁存的同时取控制信号,取控制信号的同时锁存.....

很简单的一个结构, 很容易就搞出电路然后DIY出来.

如果把ROM的位数括宽...译码都不用译了...只是不经济~

我看了网上好多单周期CPU的文章, 里面都有控制器和指令寄存器, 还有数据寄存器的锁存信号必须控制器操作,这样做增加了DIY难度 而且降低了主频, 我这里没有专门设计的控制器, 明显的特征是数据寄存器一系列暂存器件直接连接主时钟,不用经过控制器[s:427]

寄存器堆不需要数据输入的时候,会接通数据回路(寄存器输出端和输入端回路),所以寄存器不会因为上升沿到来丢失数据; 其实上面演示的是寄存器堆间数据传送的过程,数据经过ALU运算器本质上就是数据传送, 只是目标数据按规则产生了变化

我知道有人迫切的想了解单周期条件转移怎么操作, 这个后面会讲; 期间还脑残的设计了个动态分支预测机制,后来才想明白,这个机制是对CISC复杂指令的条件转移效率过低发明的~ 然后又看到ARM9里面也有分支预测.. 好无语,

未完待续....... 可能有说得不对的地方,发现的话请板砖送上~切莫被洗脑~

类似2级流水线效果图:

取指令和译码步奏合为一体,就是取控制信号,然后就是锁存,锁存的同时取控制信号,取控制信号的同时锁存.....

很简单的一个结构, 很容易就搞出电路然后DIY出来.

如果把ROM的位数括宽...译码都不用译了...只是不经济~

我看了网上好多单周期CPU的文章, 里面都有控制器和指令寄存器, 还有数据寄存器的锁存信号必须控制器操作,这样做增加了DIY难度 而且降低了主频, 我这里没有专门设计的控制器, 明显的特征是数据寄存器一系列暂存器件直接连接主时钟,不用经过控制器[s:427]

寄存器堆不需要数据输入的时候,会接通数据回路(寄存器输出端和输入端回路),所以寄存器不会因为上升沿到来丢失数据; 其实上面演示的是寄存器堆间数据传送的过程,数据经过ALU运算器本质上就是数据传送, 只是目标数据按规则产生了变化

我知道有人迫切的想了解单周期条件转移怎么操作, 这个后面会讲; 期间还脑残的设计了个动态分支预测机制,后来才想明白,这个机制是对CISC复杂指令的条件转移效率过低发明的~ 然后又看到ARM9里面也有分支预测.. 好无语,

未完待续....... 可能有说得不对的地方,发现的话请板砖送上~切莫被洗脑~

200字以内,仅用于支线交流,主线讨论请采用回复功能。