本帖最后由 神之觉醒 于 2013-10-15 18:38 编辑 基本结构:

这个东西的作用就是给个开关开关的信号(主时钟)然后就会执行ROM里面的指令,以往的自动机,要开关N次才执行完一条指令; 指令就是二进制数据, 打个比方,你可以定义00000001是自毁指令,00000010是核爆指令, 设计好之后就做电路, 然后开始运行,机器从ROM里取出为00000001的指令并执行后就机器就爆掉了,取出00000010并执行后城市就消失了= =~; 好了 不吹这么多牛逼, 实际上机器执行的指令大多只是对数据的加工, 反正就是执行指令,很简单.

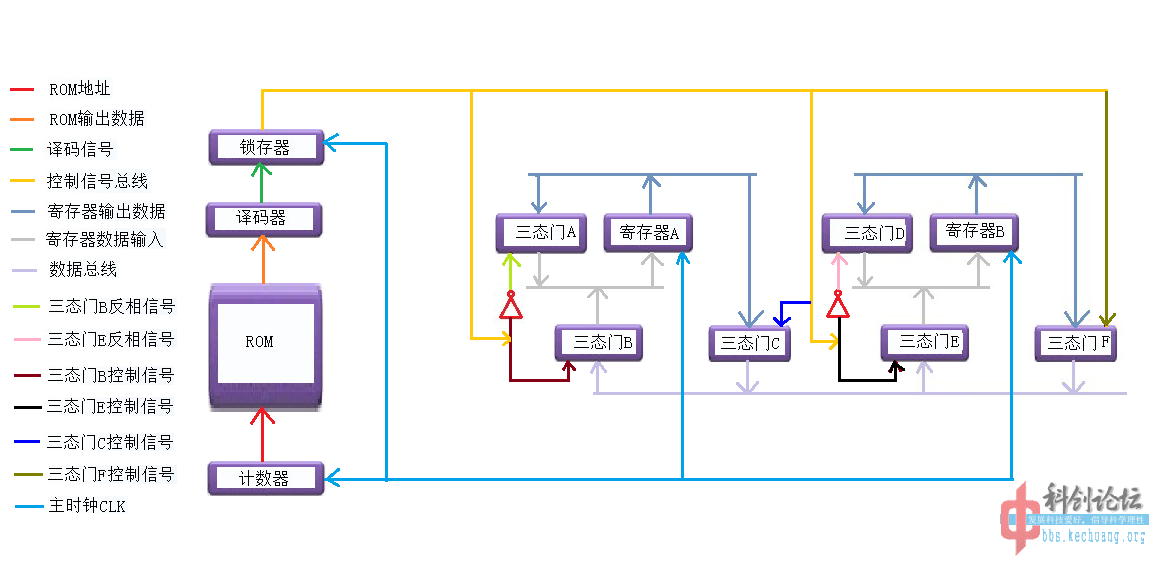

在上图这个最基本的简单结构中, 可以实现只用开关一次就可以执行完一条指令, 这里没有时序发生部件,也没有时序操作的控制部件,没有指令寄存器,没有取指令阶段,在时钟上升沿执行当前指令并锁存下条指令的控制信号,计数器、锁存器、寄存器的时钟线直接连接主时钟, 然后给主时钟输入开关信号(主频),就可以工作了。

上电:

首先接通电源,这时计数器、锁存器、寄存器的数据是混乱的,要做的第一件事就复位暂存器件的状态为全0或为全1或是指定的数据,寄存器的数据可以不复位,计数器、锁存器的数据一定要复位,在这里复位为全0,复位完成后,计数器、锁存器的数据就是0;

为了方便讲解执行过程,我在这里只定义2条指令,寄存器A到寄存器B传送指令(B = A指令)、寄存器B到寄存器A传送指令(A = B指令);然后把指令放进ROM,0地址放A = B指令,1地址放B = A指令,2地址放A = B指令;

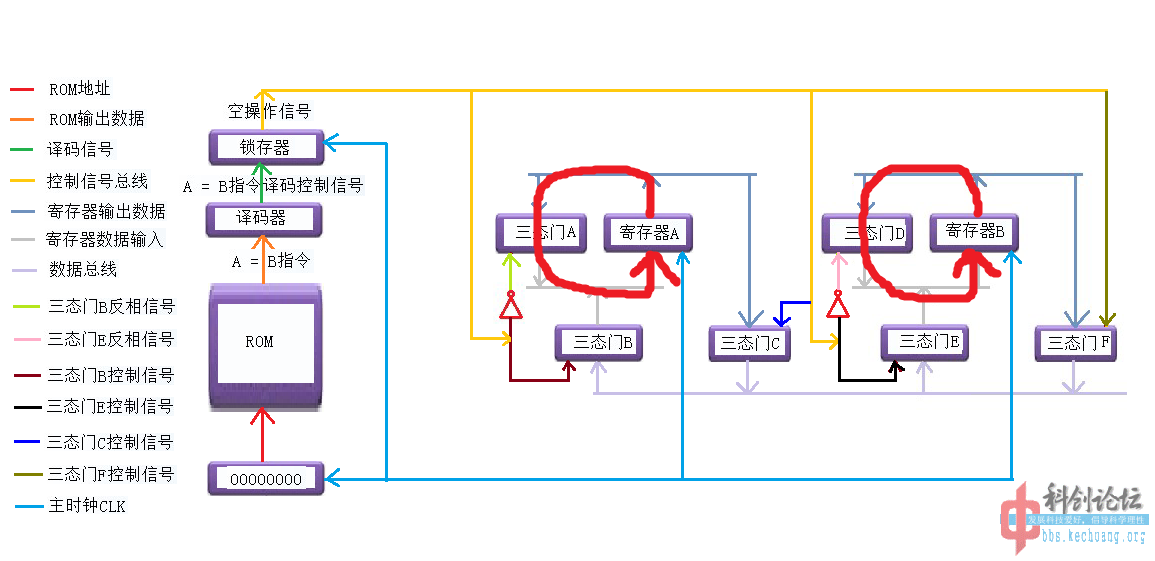

复位后的状态图示:

填流水线:

启动机器运行,需要输入开关信号(主时钟、主频),这里的开信号是上升沿,关信号是下降沿,开和关就是一个时钟周期; 现在的状态是复位后的状态(如上图所示),开始分析......锁存器输出的控制信号是全0(空操作),锁存器的输出端操作三态门的控制信号,在这里,三态门是高电平接通,低电平高阻,所以现在三态门B、C、E、F为高阻,三态门A、D接通,寄存器A寄存器B的输入端数据为其本身,计数器的数据是0,计数器指向的是ROM的0地址,ROM输出的指令是A = B指令,然后指令经过译码器译出控制信号,OK 现在A = B指令的译码信号已经送到锁存器的输入端; 这时主时钟来了一个开关信号,由于受到上升沿作用,计数器加1,指向第2条指令,锁存器锁存A = B指令的译码控制信号,寄存器A寄存器B锁存自己的数据;第1个时钟信号没有使寄存器A寄存器B的数据改变,这是因为刚开始上电复位,锁存器的数据为全0,指令还没进入流水线的缘故,第1个时钟信号的作用是填充流水线,做无用功,消耗了第1个时钟之后,后面的时钟就开始做有用功了。然后状态如下图~

![9.png]()

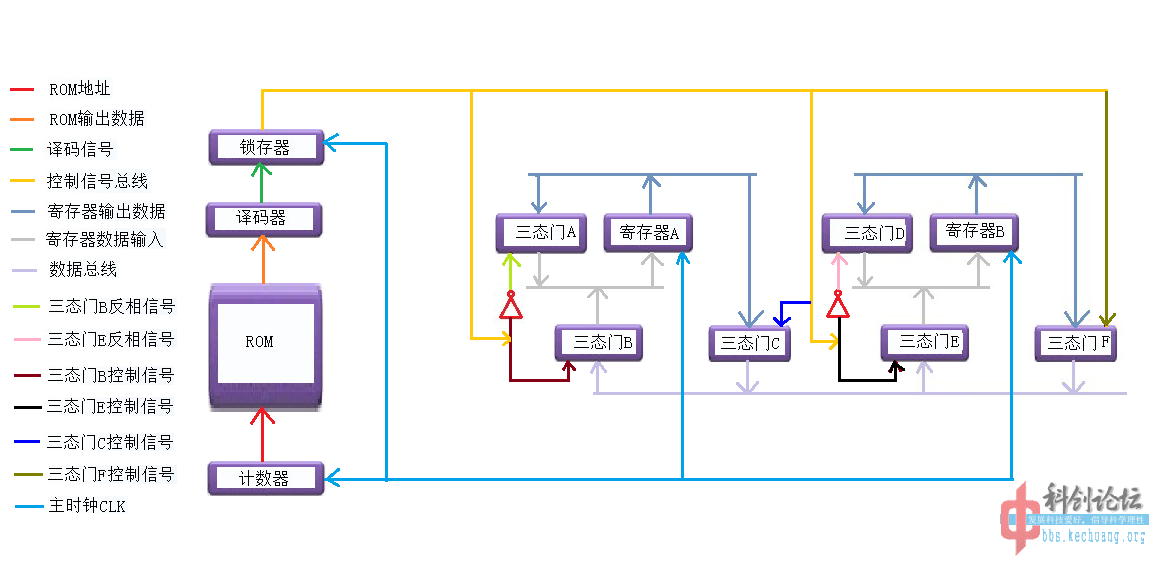

执行第1条指令:

(如上图所示)锁存器已经锁到了第1条指令A = B指令的译码信号,并且通过控制总线接通三态门B、F,三态门C、E不通,三态门A、D的状态你懂得。。。 计数器的状态现在是1,指向第2条指令B = A指令,ROM输出B = A指令,经过译码器译出B = A指令译码控制信号送到锁存器输入端,这时主时钟来一个开关信号(第2个时钟),卡擦一下。。。寄存器A锁住了寄存器B的数据(执行A = B),同时锁存器也锁住了B = A指令译码控制信号,同时计数器+1,指向第3条指令,然后状态如下图~

![10.png]()

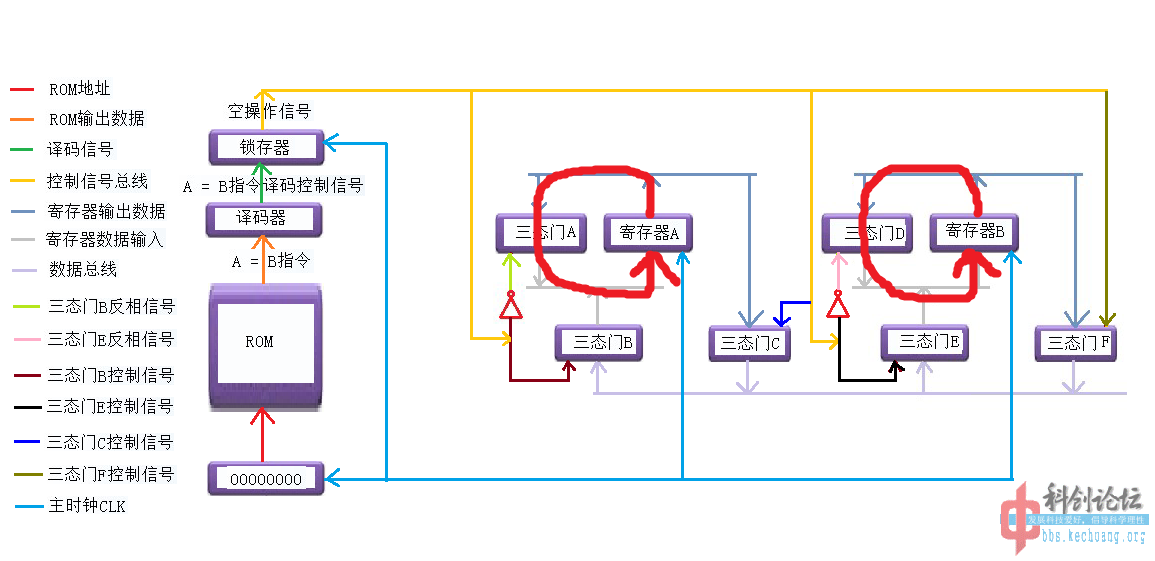

执行第2条指令:

(如上图所示)锁存器已经锁到了第2条指令B = A指令的译码信号,并且通过控制总线接通三态门C、E,三态门B、F不通,三态门A、D的状态你懂得。。。 计数器的状态现在是2,指向第3条指令A = B指令,ROM输出A = B指令,经过译码器译出A = B指令译码控制信号送到锁存器输入端,这时主时钟来一个开关信号(第3个时钟),卡擦一下。。。寄存器B锁住了寄存器A的数据(执行B = A),同时锁存器也锁住了A = B指令译码控制信号,同时计数器+1,指向第4条指令,然后状态如下图~

![11.png]()

执行第3条指令:

(如上图所示)锁存器已经锁到了第3条指令A = B指令的译码信号,并且通过控制总线接通三态门B、F,三态门C、E不通,三态门A、D的状态你懂得。。。 计数器的状态现在是3,指向第4条指令,ROM输出第4条指令,经过译码器译出第4条指令译码控制信号送到锁存器输入端,这时主时钟来一个开关信号(第4个时钟),卡擦一下。。。寄存器A锁住了寄存器B的数据(执行A = B),同时锁存器也锁住了第4条指令译码控制信号,同时计数器+1,指向第5条指令。。。然后就执行下去~~~

实际的机器结构肯定不会像第1张图那么简单,那个只是基本结构,讲解用

单周期传送指令、运算指令 、转移指令等都已经YY运行成功,目前在YY中断;

还有那台炮灰机器现在正在写程序。。。

未完待续....那个旧贴子也是

200字以内,仅用于支线交流,主线讨论请采用回复功能。