今天晚上把指令重新进行了优化 去掉了Cl/Pr的功能 多余4位作为后续可拓展指令,原来按照x86架构的想法写的寄存器所以把prcl写进去了,后来觉得根本就没必要(

前言

从今年年初的时候开始入坑数字电路直至现在已经快一年了,期间我曾尝试使用LogicCircuit软件以及logisim等软件,跟随教程绘制了x86以及mips架构等8位处理器,最近突发奇想,也想自己写一枚处理器,原本想写一枚32位的架构,后考虑到对我这种入门不久的来说难度还是太大了,于是准备写一个4位的CPU来练练手

副:评论区的视频介绍链接失效

新B站介绍视频

『手搓CPU第一期』记录用logisim进行仿真以及准备FPGA验证_哔哩哔哩_bilibili

CPU介绍

指令格式 (16 位指令集)

15-12 位 (Opcode):操作码,用于指定操作类型,支持立即数加载、减法、跳转指令及 RAM 操作功能。

11-8 位 (ALU 输入 A):连接到 ALU 的 A 输入,也可用作跳转指令的目标地址。

7 位 (ALU 输出选择):选择 ALU 的输出目标,0 表示存入寄存器组,1 表示写入 RAM。

6 位 (寄存器 CP/CR):控制寄存器是否需要触发清除 (CP) 或复位 (CR)。

5 位 (寄存器 Cl/Pr):控制寄存器是否需要清零 (Cl) 或置满 (Pr)。

4 位 (空指令):保留位,暂未定义功能,需设为 0。

3-1 位 (寄存器选择):使用 3-to-4 解码器选择目标寄存器。若寄存器信号为 100,默认选择寄存器 1,并强制使能 EN 信号。

0 位 (空指令):保留位,暂未定义功能,需设为 0。

Opcode 功能说明 (15-12 位)

0000:将立即数加载到 ALU 的 A 输入。

0001:执行 ALU 减法或加法操作。

0010:控制寄存器的读写信号。

0100:实现程序的跳转操作。

1000:用于控制 RAM 的读写操作。

支持的指令

Jump (跳转指令)

Opcode (15-12 位): 0100

功能: 实现程序的跳转操作。这个指令通过指定 ALU 输入 A 的值作为目标地址来改变程序流。跳转操作常用于实现条件跳转或无条件跳转。

Add (加法/减法操作)

Opcode (15-12 位): 0001

功能: 执行 ALU 的加法或减法操作。指令通过 ALU 输入 A 和 B 完成加法或减法运算,结果会根据 ALU 输出选择写入寄存器组或 RAM。

Load Immediate (立即数加载)

Opcode (15-12 位): 0000

功能: 将一个立即数加载到 ALU 的 A 输入端。该操作通常用于初始化或设置寄存器值。

Register Control (寄存器控制)

Opcode (15-12 位): 0010

功能: 控制寄存器的读写信号,可以通过该指令控制寄存器的读取或写入操作。通过与寄存器选择信号一起使用,可以实现灵活的寄存器操作。

RAM Control (RAM 控制)

Opcode (15-12 位): 1000

功能: 用于控制 RAM 的读写操作。该指令通过 ALU 输入选择 RAM 地址,并执行数据的读写。

Clear/Set Register (寄存器清除/置满)

功能:

寄存器清除 (Cl): 清除寄存器内容。由控制信号 寄存器 Cl/Pr (5 位) 决定。

寄存器置满 (Pr): 将寄存器置满特定值。由控制信号 寄存器 Cl/Pr (5 位) 决定。

Clear/Reset Register (寄存器清除/复位)

功能:

寄存器清除 (CP): 通过寄存器的清除控制信号清除寄存器内容。

寄存器复位 (CR): 将寄存器重置为初始状态,通过控制信号决定。

Register Selection (寄存器选择)

功能:

使用 3-to-4 解码器根据指令中的寄存器选择字段 (3-1 位) 选择目标寄存器,并通过控制信号使能该寄存器。

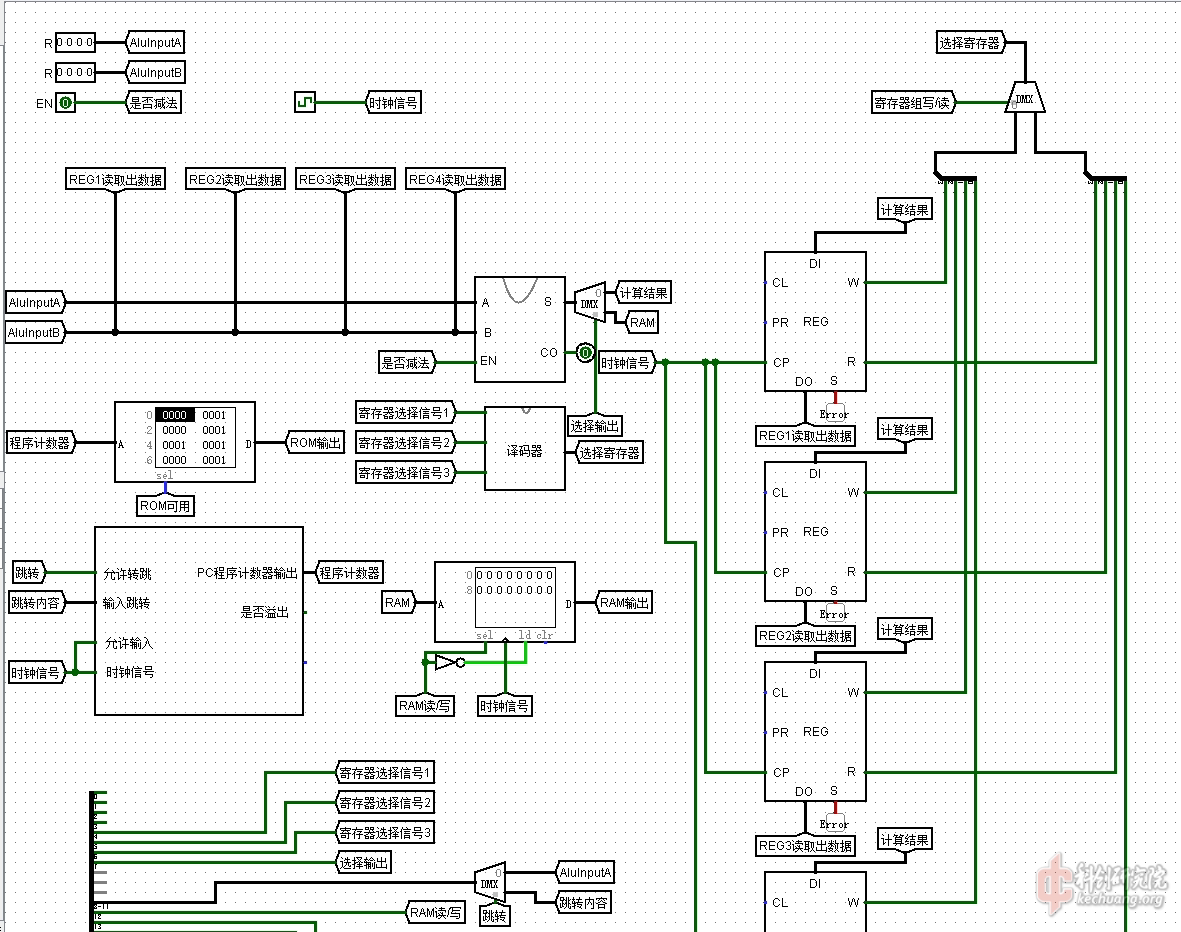

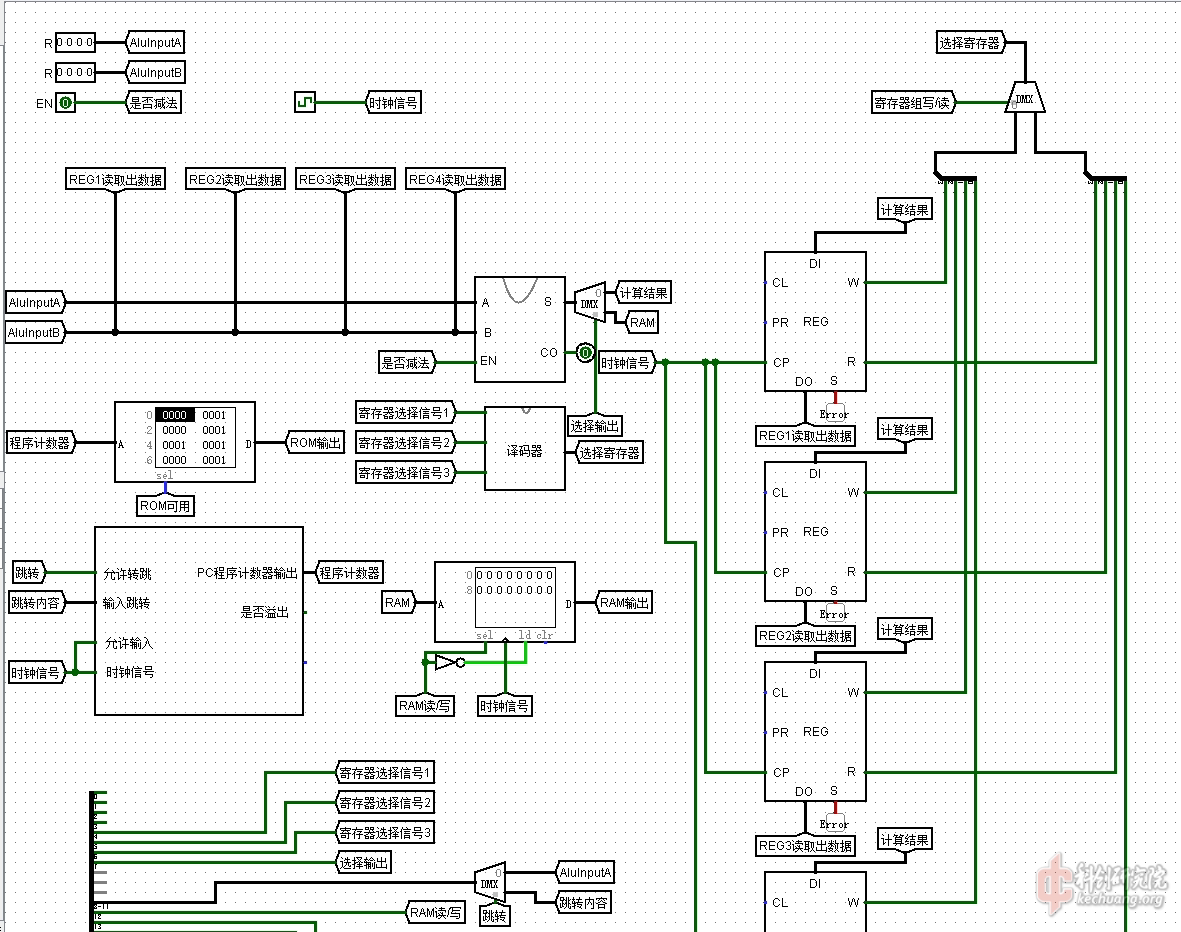

logisi设计图

下图为整体的设计

接下来具体介绍部分模块

上图为REG(寄存器组)模块 通过点对点连接直接连接到ALU部分 当ALU完成运算后会把运算结果同时给予给四个寄存器,但是只有在W信号为高电平(1)时,相对应的寄存器才会把收到的计算结果写入,否则即使收到ALU计算机结果也不会写入寄存器中(当然也可以把数据写到RAM)

上图为ALU模块,当收到立即数指令之后,指令集中会有四位输出给予给ALU的A输入,然后再将A直接通过ALU输出给寄存器组模块,当需要完成1+2的操作时,需要将寄存器组的内容取出然后输出给ALU B输入,然后再与立即数2进行相加操作。对于例如5+5的操作,每次都需要先把第一个加数写入寄存器后再拿出来和另一个立即数进行相加运算(个人感觉繁琐了),原本准备设计一个专用寄存器给ALU进行运算而不调用寄存器组,后来觉得太麻烦就把这个想法抛弃了。

上图我们介绍一下转跳指令,当指令为0010,即为转跳指令时,用于立即数输入的四位指令会变成转跳指令,其四位输出会作为转跳指令输出给PC程序计数器而不是ALU模块。

以上就是整个CPU架构的介绍了,现在整个u都还有很多bug,例如ram部分我到现在才发现它的输出没连(bushi

也欢迎各位提出意见

[修改于 7天17时前 - 2024/11/26 23:50:16]

今天晚上把指令重新进行了优化 去掉了Cl/Pr的功能 多余4位作为后续可拓展指令,原来按照x86架构的想法写的寄存器所以把prcl写进去了,后来觉得根本就没必要(

mips和x86都是32位的, 其实如果用软件模拟或者FPGA实现, 32位是最简单的

mips和x86都是32位的, 其实如果用软件模拟或者FPGA实现, 32位是最简单的

以前有试着用fpga去写rv32 但是听了两节课之后就没坚持下来,另外我跟着做的两节课还原的x86和mips都是八位的处理器 但是用的32位指令集

推荐一个学习网站 https://nandgame.com/ 把CPU设计成一个闯关游戏,从最基础的与非门开始构建

最简单并且功能完善,具有实用价值的是 J1,一个面向forth语言的堆栈处理器,

鸡肋的一点是,用forth写代码比用逻辑搭这个CPU都累人,forth 真的是和汇编同等的低级语言

推荐一个学习网站 XXXXXXXXXXXXXXXXXXXX/ 把CPU设计成一个闯关游戏,从最基础

感谢推荐 相似的游戏还有steam上的图灵完备 那个也是从最基本的门电路开始搭建 还有沙盒模式可以随便写cpu 我印象里好像还可以导出verilog语言,不过有点小贵 我花了70大洋原价买的

建议是初学者不要尝试设计冯诺依曼架构, 即代码和数据放在一块的, 会非常坑爹,我用Verilog实现已经非常头疼了,用器件搭建会更加头痛

实现哈佛架构, 即代码和数据分开的, 会简单也便于处理一些

| 时段 | 个数 |

|---|---|

| {{f.startingTime}}点 - {{f.endTime}}点 | {{f.fileCount}} |

200字以内,仅用于支线交流,主线讨论请采用回复功能。