非常好的分享,让我想起原来做CC2640超低功耗方案的时候。

外控一个MCU,所有系统都属于DISABLE依然有耗电,后来才怀疑到一个IO的内部嵌位,很多时候都不会在等效电路表示。

但是很多IC为了保护端口电平都有这个设计,后面我就全部用一个PMOS彻底隔断供电OK了

硬件设计工作小白一个 ,今天在测试板子的时候发现在原理图设计时踩了几个“坑”。发上来与大家分享一下。

,今天在测试板子的时候发现在原理图设计时踩了几个“坑”。发上来与大家分享一下。

简述背景:

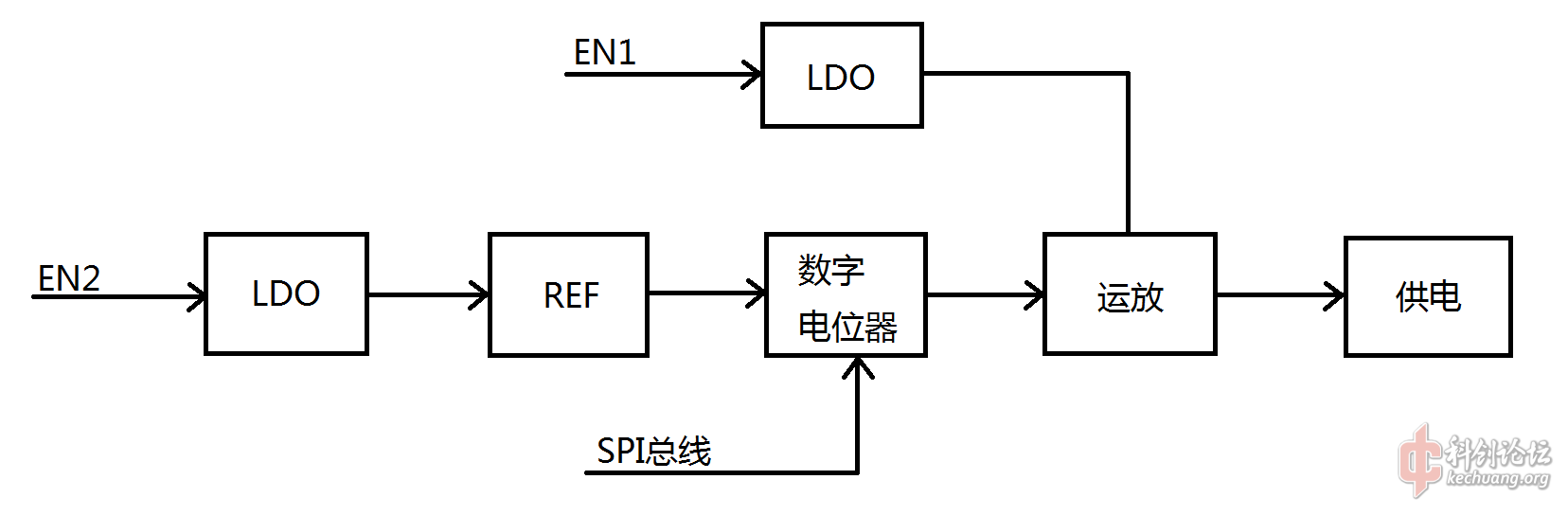

某个器件需要多路偏压,同时对这几路偏压的上电时序有要求。其中一路电压可变偏压的框架设计如下图所示。

大致的思路为电压基准源给数字电位器供电,SPI总线配置数字电位器改变中间抽头的位置以改变其输出电压值,然后使用运放做跟随和滤波,运放输出给器件供电。由于运放没有EN脚,只好选择控制运放的供电LDO(EN1)。

“坑”位2:在“坑”位1的基础上,测量数字电位器的输出为5V,过了一级LPF(R=10K,C=10uF)后到达运放的+输入端居然只有1.3V,不供电的状态下输入端呈现低阻状态?

“坑”位3:EN2拉低,电压基准源不供电,测量电压基准源的输出端存在2.7V的电压?

大致分析:

前面两个问题都与运放有关,运放型号为LT6203。datasheet如下:

设计的时候简单的认为运放不供电,那其输入端和输出端应该为隔离状态。然而看了运放内部的简化图后:

运放的+输入端和-输入端存在D1和D2两个二极管,用于保护其正负输入端的电压差不超过±0.7V(随便取了理论值,实际上与电流有关)。那么运放在不供电时,正负输入端也不是隔离的。而运放是接为跟随器使用,因此运放的输出端也存在电压。

而“坑“位3的情况,则是由于SPI总线在不使用时,nCS与SCLK同时都拉高(FPGA的SPI内核模式选择决定的),而SPI总线是3.3V电平,在EN2拉低后,IO引脚上的电压倒灌到了数字电位器的电源上。该数字电位器的内部结构图不得而知。这一问题的解决只能是在数字电位器不供电情况下,配置FPGA的SPI IO口直接拉低,在供电后再释放。以避免IO电压倒灌的现象。

以上就是分享的全部内容。分析部分若有错误,请帮忙指出,不胜感激。

这些大大小小的坑,在我的职业道路上能给我积累和进步。遇到问题,分析总结,避免再犯,才能在这条路上迈进一步。

非常好的分享,让我想起原来做CC2640超低功耗方案的时候。

外控一个MCU,所有系统都属于DISABLE依然有耗电,后来才怀疑到一个IO的内部嵌位,很多时候都不会在等效电路表示。

但是很多IC为了保护端口电平都有这个设计,后面我就全部用一个PMOS彻底隔断供电OK了

其实opa手册写了输入最大范围一般是,是+VCC+0.xV 和-VCC -0.xV。

这个不给电给输入其实算是超参使用。

引用1176764177发表于3楼的内容其实opa手册写了输入最大范围一般是,是+VCC+0.xV 和-VCC -0.xV。 这个不给电给输...

嗯对,从这个方面考虑的确是超参数使用了。

我发了一个帖子,分享了一个应用手册里面有讲到这个问题。

200字以内,仅用于支线交流,主线讨论请采用回复功能。