没人鸟。。这用来做交替采样ADC组成示波器再合适不过了,只不过要4个PLL

59331

%7B%22isLastPage%22%3Atrue%2C%22notes%22%3A%5B%5D%2C%22pid%22%3A%22t59331%22%2C%22tid%22%3A%2259331%22%2C%22mainForumsId%22%3A%5B%2237%22%5D%2C%22categoriesId%22%3A%5B%220%22%5D%2C%22tcId%22%3A%5B%5D%7D

%7B%22isEditMode%22%3Afalse%7D

【原创】FPGA内部利用PLL级联实现10ps级可编程延时控制

利用Cyclone IV/III/II 中PLL级联实现产生一路10ps级精确相移控制的CLK信号,输入频率范围5~400MHZ,输出最高1.2GHZ。

专用可编程延时芯片也可以实现这样的功能,例如AD9501.但是9501频率<50MHZ并且停产多年,价格50CNY/片。采用机械游标延时(精确控制导线长度)体积巨大,不可编程。

FPGA、CPLD的门延时,例如一个buffer,造成的延时都>1ns,并且随温度、电压而急剧变化,最多可以翻倍。

Cyclone IV PLL本身也能实现最小96ps相移,但是输出频率上升,步进就增大(250MHZ输出时步进为0.25ns),这对于一些时间交替采样ADC系统来说实在不够精确。

对于上升时间3.5ns的信号,利用两片8位ADC进行交替采样,即便只是20ps的采样时钟误差,也能使有效位数下降到7位。

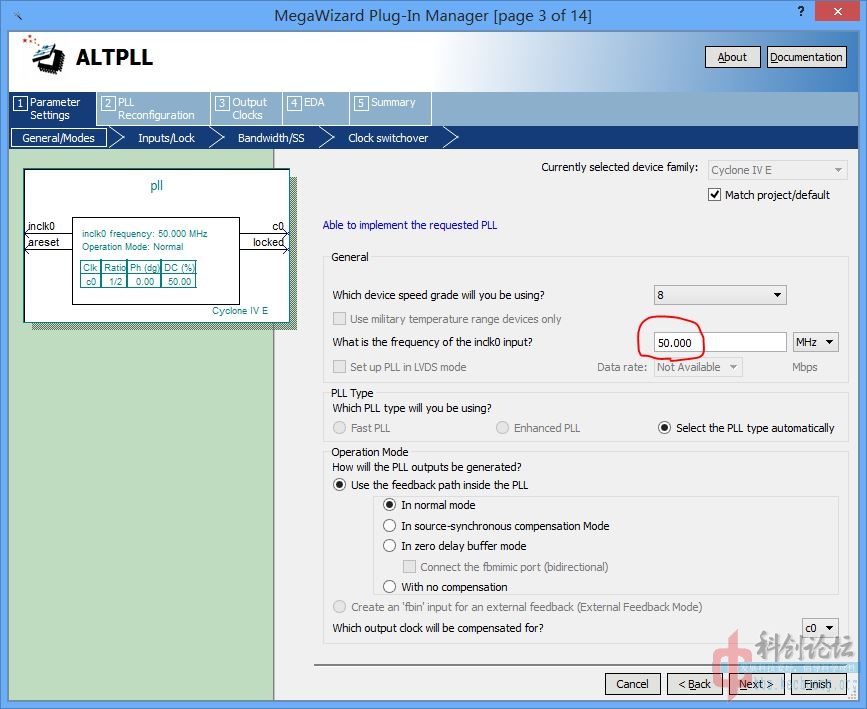

设置需要的输入频率,模式设为正常

![1.jpg]()

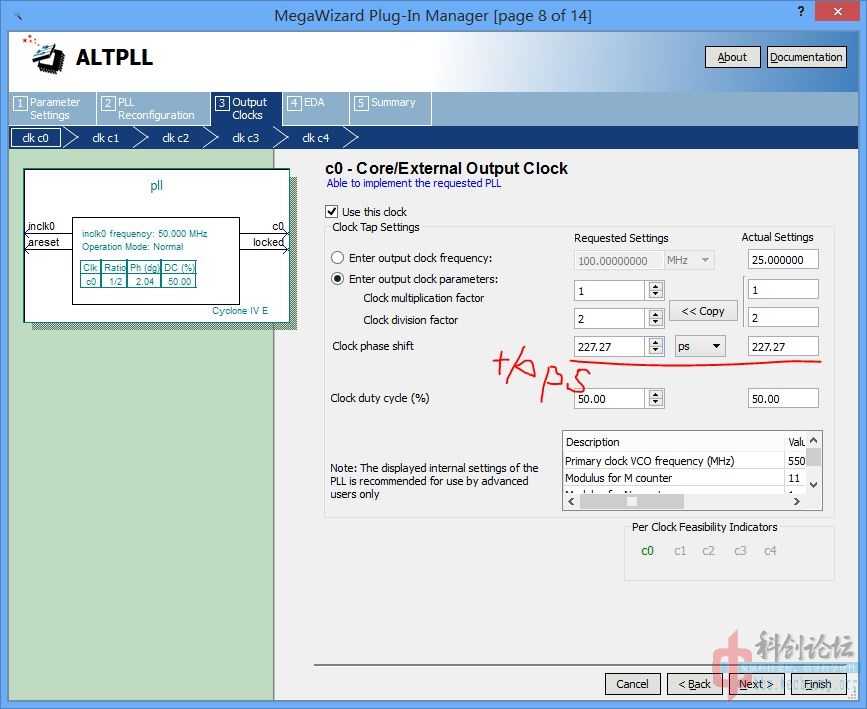

进行二分频,力图使VCO频率为600MHZ,再clock phase shift中设置需要的延时(相移)

![2.jpg]()

测试一下,227.27-217.39<10ps

![3.jpg]()

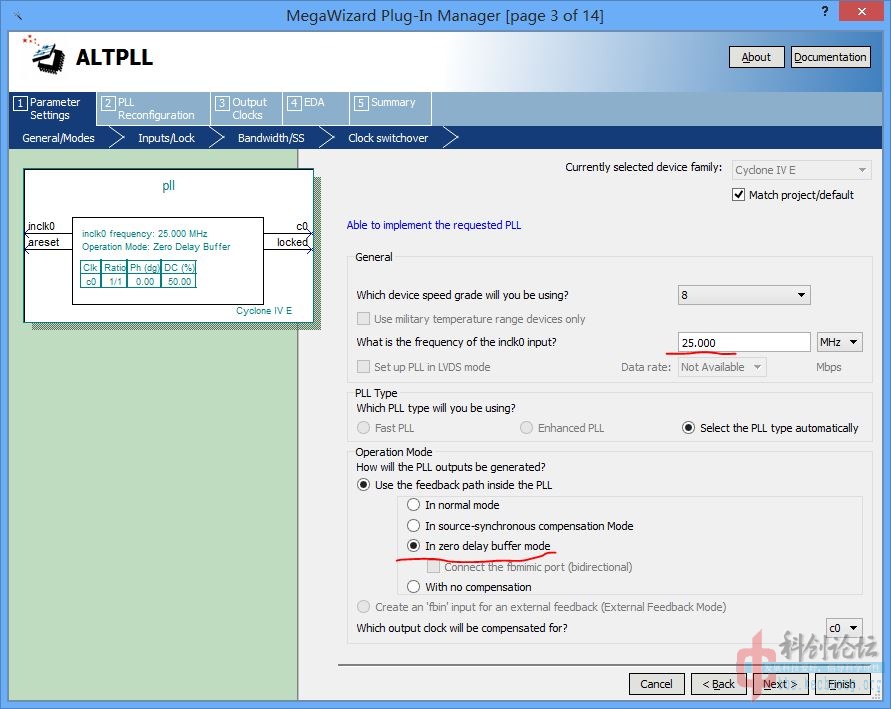

再兴建PLL2,输入频率设为PLL1的输出频率,两PLL通过全局时钟网络直接相连

模式设为零延时

![4.jpg]()

倍频到需要的频率

![5.jpg]()

专用可编程延时芯片也可以实现这样的功能,例如AD9501.但是9501频率<50MHZ并且停产多年,价格50CNY/片。采用机械游标延时(精确控制导线长度)体积巨大,不可编程。

FPGA、CPLD的门延时,例如一个buffer,造成的延时都>1ns,并且随温度、电压而急剧变化,最多可以翻倍。

Cyclone IV PLL本身也能实现最小96ps相移,但是输出频率上升,步进就增大(250MHZ输出时步进为0.25ns),这对于一些时间交替采样ADC系统来说实在不够精确。

对于上升时间3.5ns的信号,利用两片8位ADC进行交替采样,即便只是20ps的采样时钟误差,也能使有效位数下降到7位。

设置需要的输入频率,模式设为正常

进行二分频,力图使VCO频率为600MHZ,再clock phase shift中设置需要的延时(相移)

测试一下,227.27-217.39<10ps

再兴建PLL2,输入频率设为PLL1的输出频率,两PLL通过全局时钟网络直接相连

模式设为零延时

倍频到需要的频率

回 1楼(大圈圈) 的帖子

你考虑过fpga输出时钟的jitter吗?如果你的采样频率和输入的信号很高的话,这个jitter是你忍受不了的。

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 2楼(djc001) 的帖子

肯定小不了,具体值看输入时钟,100mhz模拟输入以上必须加ad9510去抖

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

回 2楼(djc001) 的帖子

即便是AD9513 1.5ns满量程16级精调,也只能93ps步进啊 [s:269]

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。