一直有打造一台计算机系统的想法,恰巧今年有机会,就开始了设计。我的目标是能够运行,用74门搭建,而不仅仅是仿真或在FPGA上运行(主要是我不会hh)。构思了一段时间,把整台机器的架构稍微梳理了一下。画了一个思维导图,大家凑合看。涉及到运算,一定会有位宽这一概念。这台计算机设计出来的目标是运行,不仅仅是软件上的设计,于是74门的数量就是个大问题。大家知道,计算机的位宽增加,晶体管的数量必然成指数型增加,划不来。现在拿性能换成本,抛弃性能,做成一位的,74门数量可以做到几十片甚至十几片。

![image.png]()

首先是CPU

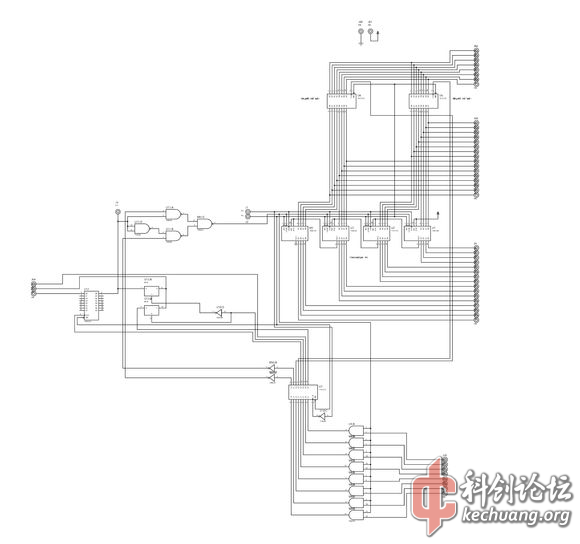

实际上,CPU的开发工作在几个月前就开始了,几年前也有过做CPU的想法,也构思过一段时间。成本限制,现在目前设计了16位程序指针,可以寻址64k字节的程序代码。CPU涉及到跳转指令,所以使用74hc161这种可预置的二进制计数器作为程序指针,共需4片。cpu采用超精简设计,由于只有一位位宽,在操作内存过程中没有字节的概念,直接操作位。这样虽然效率较低,但硬件简便。CPU没有片上alu,只提供立即数放内存、读取内存、内存移内存精简指令,把alu逻辑运算单元当作内存的一部分操作,如思维导图。cpu使用16位指令集,低八位数据,高八位指令。低八位在跳转指令时先分别向两个程序地址寄存器中送入数据,耗时两个时钟,再跳转,耗时两个时钟。共耗时四个时钟。

片内所有的寄存器,包括内存数据暂存器、指令暂存器、两片程序地址暂存器,都使用了74hc273这种上升沿D触发器。指令译码部分其实有点像自动机,每次译码要先给主时钟,PC+1,等地址和数据建立完毕后再拉高指令锁存,然后全0为不动作(空指令),看哪位有1就执行相应的动作。按照这个逻辑,指令锁存要比PC时钟迟一些到来,所以给指令暂存器的锁存端口加一个非门。这样主时钟上升时建立地址,稳定后时钟下降,地址锁住不变,此时对于指令暂存器来说时钟是上升的,指令被锁住,完成译码。

构思CPU有三种跳转方式,分别是目标地址跳转、DB总线接口为1跳转、DB总线接口为0跳转。目标地址跳转需要两个时钟周期,判断跳转需要1+2=3个时钟周期,若不跳转只消耗2个时钟周期。因为内存里的数据需要读取到暂存器,所以这会占用一个时钟。判断跳转那个地方使用四个与非门,根据电路图不难了解原理。

![image.png]()

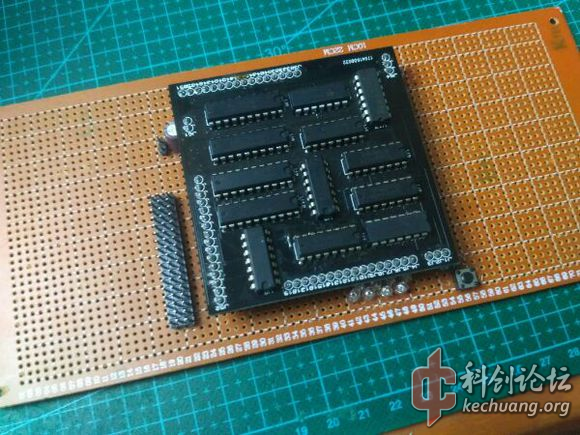

CPU设计完毕后打了一张板子,把基本的功能之类都测试一遍,发现功能正常。下面放一波图

![image.png]()

![image.png]()

![image.png]()

图为测试板

测试得出一点:所有把数据移入某个寄存器的指令后面必须不能是把数据移入这个寄存器的指令(例如数据移ra后,下一个时钟周期不能再次移ra),因为移入时寄存器的时钟需要上升沿才能有效,而两次移入会导致时钟没有拉低缓冲时间。

将CPU的指令汇总一下,就有了指令集。真正的精简指令,只有10条(也可以认为是我偷懒了

RA是高八位地址寄存器

RB是低八位地址寄存器

xx表示任意数据

aa表示地址数据

高位 低位

单字节:

0x00 0xxx 空指令

0x80 0xxx DB为1时跳转到RA RB

0x40 0xxx DB为0时跳转到RA RB

0xC0 0xxx 无条件跳转到RA RB

0x20 0xaa 地址数据送RA

0x10 0xaa 地址数据送RB

0x08 0xxx RARB指向RAM送RC

双字节:

0x04 0xxx┐

0x06 0xxx┴ RARB指向RAM置0

0x05 0xxx┐

0x07 0xxx┴ RARB指向RAM置1

0x00 0xxx┐

0x02 0xxx┴ RC送RARB指向RAM

注:RAM区不使用标准结构,使用上升沿D锁存器构成储存单元,寻址空间0~2^16-1=0~65535

然后就是构成计算机系统了。RAM使用74HC74+(74hc138+4016传输门)译码,ROM是at28c256。这些确定了就可以打主板了。没想着做多少性能,就只用了4片74HC74构成1*8的内存空间,ROM有16*32K空间,两者最多均可寻址64K。io部分就偷懒吧,直接把内存的输出引出来,接个led也可以显示工作状态,没有设计输入接口。

![image.png]()

![image.png]()

这是整个计算机系统的pcb,已经设计好送去打样了,还没到手。布线很乱,大家也不要喷了,因为这个电路相对来说还是有点麻烦的,于是自动布线爽歪歪。毕竟板子不想跑高频,主频10K差不多了,虽然74门最多可以支持10M,不过也无所谓啦。现在板子上不带时钟,用按钮按,时钟有引出,可以外加。

好吧,今天先写这么多,等全部测试完毕后再来补吧。电路图不在身边,下次再发。

200字以内,仅用于支线交流,主线讨论请采用回复功能。