楼主的设计令人感到全身温暖、血脉喷张!

当然我回帖一向都是以吐槽为主的。下面开始。

1.好贵的管子呀

按照400V/2kW来算,二极管平均电流是5安,rhrp3060在5安的压降是1.2V,即消耗 6W。

占空比不清楚,暂且设mos最大电流10安,50%占空比。双mos并联后导通电阻为35毫欧,即消耗3.5W。

此管Cgd Cgs非常大,400V Vds下开关损耗极其可观,建议楼主计算一下双管并联的开关损耗。如果忽略开关损耗,楼主双mos并联,导通损耗3.5W左右,平均每个管子小于1W,等于完全不用加散热片(就算加也不用加那么大一块)。

2.设计总是很复杂

虽然运放和贴片电阻都很便宜且很可靠,但大量使用仍然不利于MTBF。

有一些电路设计,更是复杂得匪夷所思。

挑一例典型的,批评一下:

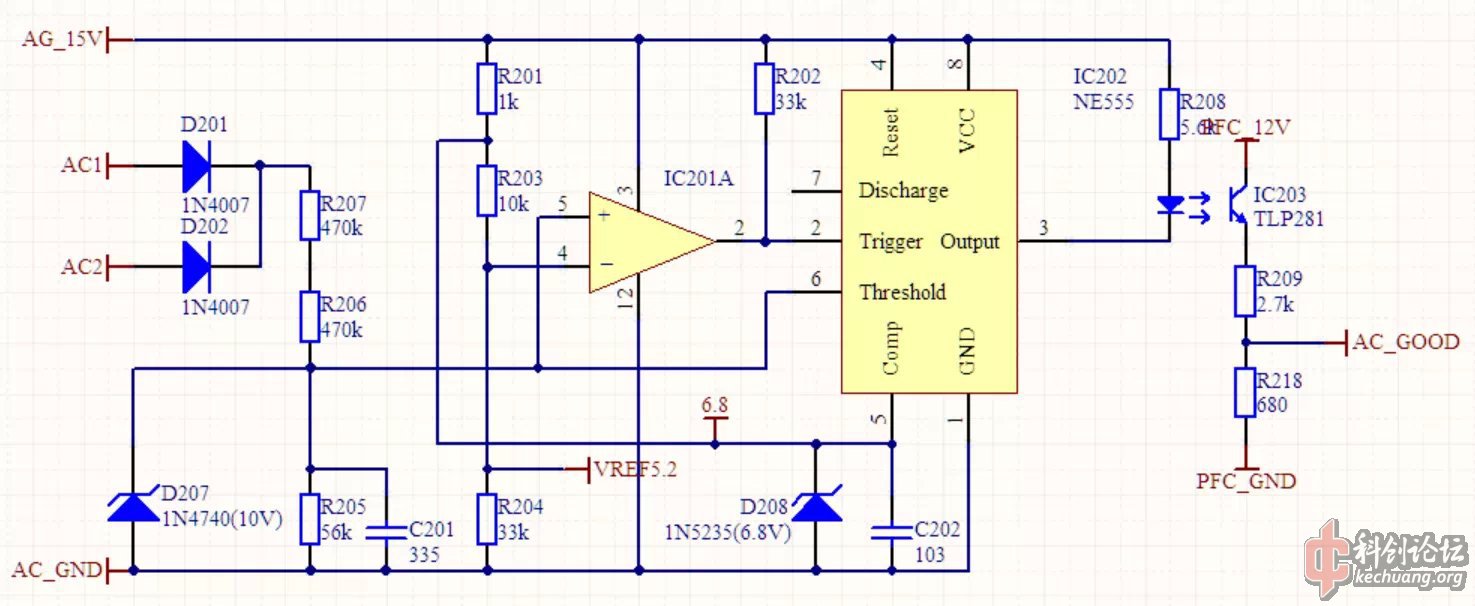

楼主的目的:threshold电压大于6.8光耦通电,小于5.2光耦断电。也就是一个滞回比较器。

首先齐纳管分压完全不需要旁路电容,15V上面的100mV噪声用齐纳+电阻分压之后不会大于5mV,完全不影响滞回比较器(比较区间1.6V)工作。

其次,滞回比较器完全不需要使用555. 下面这个电路可以实现一样的功能。

![QQ截图20150104014623.jpg]()

5V直接用15V分压就行了。

如果再要找茬,就是为了电压检测这么一个功能而专门加一路供电,是不是太多余?

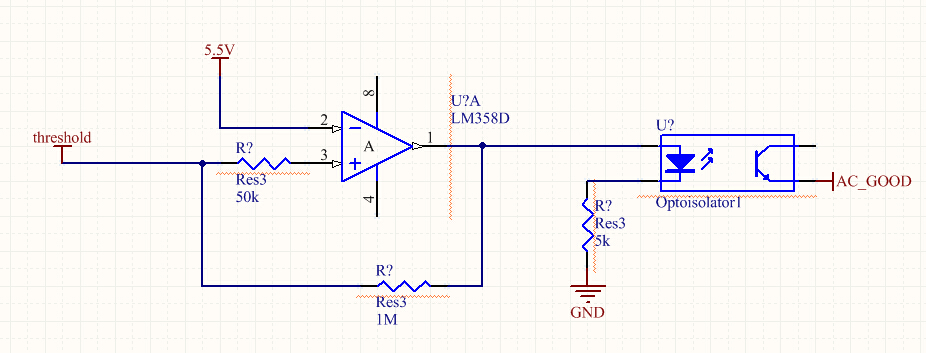

![QQ截图20150104025519.jpg]()

输出RC滤波,再接比较器即可。图中有错,GND改成AC2,要串4007

此电路工作原理:如果交流输入电压的1/100大于发光二极管导通电压,则光敏三极管一边会产生电流。

如果需要设置很精确的低压门限,当幅值超过门限时光耦输出脉冲信号,则可考虑TL431。

个人意见:如果纯粹为了保护管子,漏极用康铜丝采样,过流保护即可。

3. gate drive

12V驱动电压+10欧串联电阻=最大驱动电流1.2A,因此驱动用IR2110即可(一片可管两个通道),不需要具有12A输出能力的MIC4452。

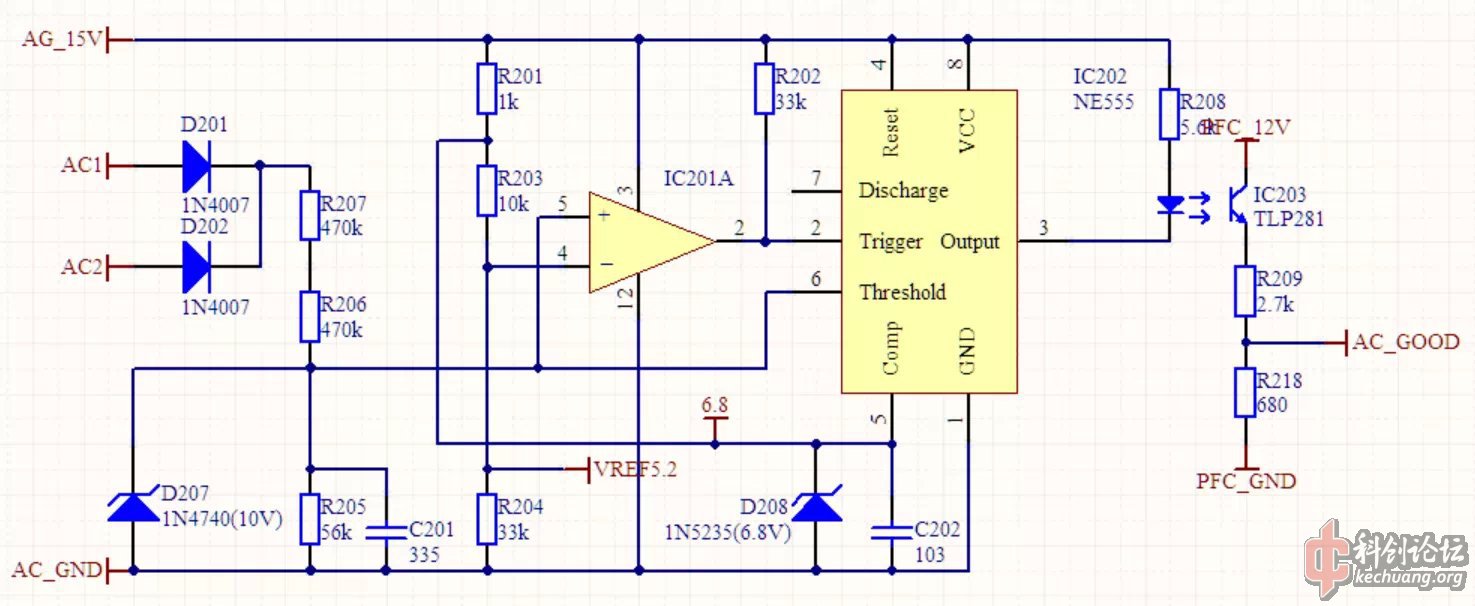

关断有二极管加速,看似万事大吉,但楼主的gate离drain太近,离source太远,寄生Cgd电容会导致excessive ringing;且gate drive return没有单独连到每个管子的source,而是从一大片铺铜返回,这会导致gatedrive 的回路面积增加,首先EMI会通不过,其次gate drive路径寄生电感增加,同样会导致excessive ringing。

![37_23215_13cc67f9b764298.jpg]()

图中黄线就是12A驱动电流将要流过的路径。

建议楼主发个Vgs和Vds波形让大家欣赏下。

除了这一处之外,其他大电流回路的走线还是比较合理的。

4. 铜皮和走线的阻焊可以直接勾选开窗,无需事后再加。

5. 人无完人,楼主万岁万岁万万岁