会长期关注

我平时只是去用这些IC 刚好可以了解一下具体的设计流程

该设计由如下几个部分构成:

1.VCO 压控振荡器

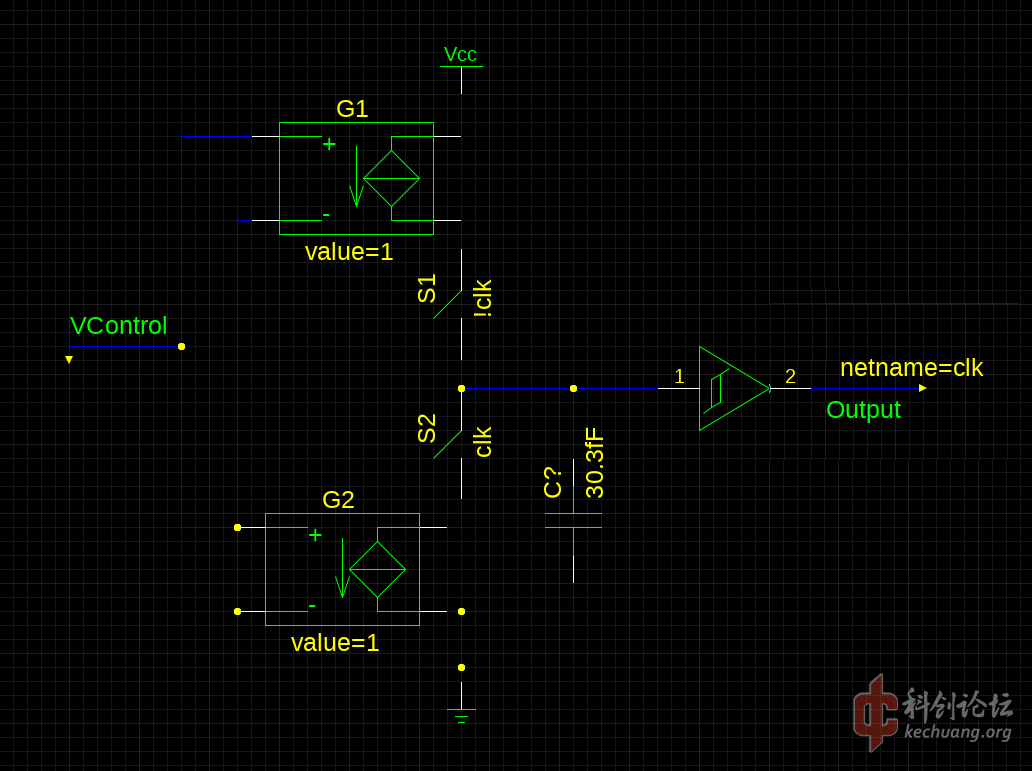

该部分作为内置振荡器,由一个张驰振荡器构成,其理想模型如下:

2.PFD 鉴相/鉴频器

该部分检测输入和输出的相位差和频率差,并反馈给VCO

计划使用传统的双D触发器PFD,延迟约5级反相器延迟

该部分暂未开始设计。。。。

3.LPF 环路低通滤波器

该部分将PFD输出的信号低通滤波之后产生Vcontrol信号,供给VCO

参考拉扎维的《模拟CMOS集成电路设计》,计划使用电流源配合电荷泵的结构。

很遗憾,暂未开始设计。。。

第一部分:VCO 的设计

接下来的所有手工分析基于SPICE Level1模型。

在CMOS设计中,我们使用电流镜作为电流源

已知

可得(在沟道长度和工艺条件一致的情况下)

模拟开关在这里则使用一个简单的非门

那么仿真结果呢?

这不是最严重的问题,当继续减小参考电流,会出现两个问题(如下图所示,参考电流5uA):

1.振荡频率并没有如同我们想得那样线性的下降

2.输出的占空比会发生显著的变化

3.施密特触发器的触发电压发生了变化(这个我暂时没分析出原因)

从两个开关管的电流波形中,可以看出一些端倪

对两个电流源管的VD进行仿真,可以发现两个电流源管经历了从线性区到饱和区的转变过程,这解释了为什么这两个电流源工作的如此之差。

占空比问题的解决:上图中N电流源管的尺寸是P管的1/2(当时考虑到电子迁移率是空穴的2倍),但是没考虑到MOS管寄生的电容,将N管尺寸扩大之后占空比问题得到了解决。

电流源问题的解决思路:

1.想办法让电流源管永远工作在饱和区(有限的分析显示要么以功耗为代价,要么不可能)

2.在电流源设计中,在电流镜本身加入使能端(这对电流源电路提出了较高的要求)

3.更换电路结构

在接下来的帖子中,我会试图手工对现在这个电路进行有限的定量分析,以及参考current steering DAC中开关电流源的设计给这个VCO设计出一个更好的解决方案,补充Bias Current Generator和输出滤波器的设计。

一个暂时的后记:

为什么要做这个设计?我承认用张驰振荡器作为PLL的核心是一件非常蠢的设计,蠢到在网上几乎无法搜到相关的论文。但是,如果成了,证明就算是蠢设计,精良的设计也可以让它达到可用的地步;成不了,证明蠢设计永远是蠢设计,坑,别踩。无论如何,我能证明点事情,不是吗?

这个腦洞怎么来的?一方面是初学者的初生牛犊不怕虎,另外呢,是和大光同学开玩笑的时候想到的去设计一些去“加速老板破产”的设计,一个是这个,最后我希望它能被优化到可以用在一片山寨版R820T里本振的地步,另一个就是山寨一片AD9361,用环形振荡器做PLL。所以,这个系列能写的东西非常多,时间跨度会非常长

最后说句老实话,本人只是一个初学者,基础知识比较缺乏,而且如各位所见,在设计中遇到了不少的问题,所以,这个帖子会更新的比较慢,与其说是一个项目展示,不如说是踩坑笔记,很多的定性分析和相关仿真我会在之后慢慢补齐,还请各位看官见谅。如果论坛里有搞模拟IC设计的朋友在此加以点拨,鄙人谨表欢迎,如有错误,还请各位不吝斧正。

睡了睡了。

[修改于 7 年前 - 2018/09/23 23:28:53]

会长期关注

我平时只是去用这些IC 刚好可以了解一下具体的设计流程

继续定性分析如下:

结合模拟集成电路设计精粹中给出的曲线可以看出,误差主要来自于2部分:

1.沟道长度调制效应会导致在对电容充电的时候电流会出现轻微的变化

2.管子从线性区向饱和区转变的时候gm急剧的变化导致电流的尖峰

经过这两天的资料搜索,参考上面的文献,我完成了VCont-FreqOut曲线的仿真,仿真结果表明,最简单的思路是,我可能需要将这个设计改成几个分段的电流源来提供电流输入。

由线性区的公式,

我们可以得出这样的结论:电流源管进入线性区是应当绝对避免的

那么,正确的方式应当是将电流源管关断,更新后的电路如下:

我们可以看到,图中PM0和NM0的作用就是关断对应的电流源。

经仿真可见,这种电路结构效果拔群

另外说一句:这个VCO的设计可能不会出现在最终的结果中,它会进一步的向低频,低功耗方向优化,用于一个VCO ADC