恭喜,三个月的努力终于让国内玩家玩上了新东西。

81569

%7B%22isLastPage%22%3Atrue%2C%22notes%22%3A%5B%5D%2C%22pid%22%3A%22832110%22%2C%22tid%22%3A%2281569%22%2C%22mainForumsId%22%3A%5B%22139%22%5D%2C%22categoriesId%22%3A%5B%22437%22%5D%2C%22tcId%22%3A%5B14%5D%7D

%7B%22isEditMode%22%3Afalse%7D

“云豹”跳脉冲驱动板(SKP DRIVER)是如何被研发出来的?

今年年前,在4hv看到了关于“跳脉冲”驱动的帖子。

觉得非常有意思,其原理在之前的帖子里已经发了。

XXXXXXXXXXXXXXXXXXXXXXXX/t/81286

鉴于需求比较清晰,所以开发起来就有了方向。

由于跳脉冲驱动模式比较特殊,也没有人用分立电路的形式设计一款合适的驱动电路。

所以我便萌生了使用可编程逻辑器件来实现驱动的意向,其实skp模式的需求主要可以分化如下。

1:保持DR4-1.3b系列具有的一切特性,同步灭弧、关断。

2:拥有过流后,发生一次跳脉冲而非直接关断的新特性。

——

由于谐振驱动电路的特性,所以一切操作都必须遵循过零点切换。

了解到以上特征,我年前花了两天时间,用verilog写了几百行代码。

初步实现了DR4-1.3b移植到CPLD上,这也算是一个里程碑。

![1.png]()

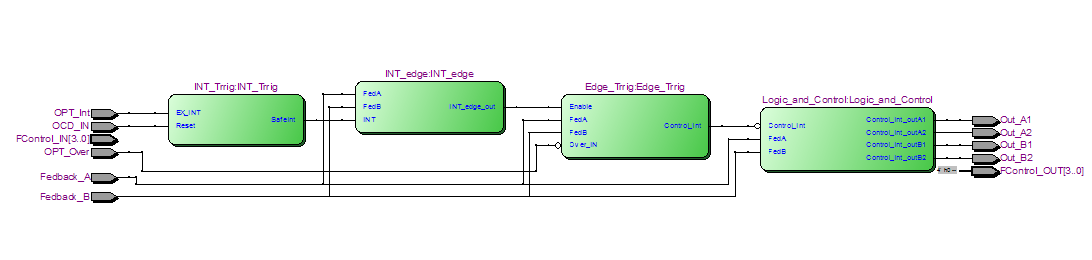

可以看到综合出来的这一段RTL一共可以分为四个模块。

前两个模块是对灭弧和反馈信号做同步,最后一个模块是能够在发生skp的时候。

交替关断,均摊发热量。

![2.png]()

寥寥四个模块,就构成了skp的基本功能形式。图中看出,skp功能已经被实现。

但是依然存在一些问题。

其中核心代码分享如下

这个模块产生了一个以FB信号更新的上升、下降沿D触发器。

实现基本skp功能。

——

篇幅有限 ——时光如流水,无数个昼夜,三个月之后->

——

![3.png]()

它更新到了V2.3beta

![4.png]()

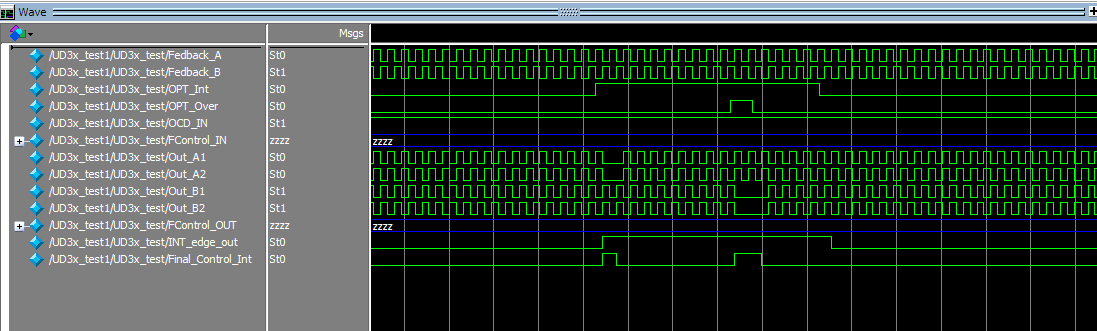

RTL综合如下。

![5.png]()

最终功能全部完善,能够完全不要模拟外围实现逻辑功能。

代码也比当时翻了三倍,但一切的努力都没有白费。

![IMG_1079.jpg]()

在高压局和工业局各位同志热心的帮助下,这款skp驱动板终于以硬件的形式呈现在我的面前。

这里要特别感谢袁局(review) 、NPK(logo)、虎哥(suggest)和我的妹子(logo)provide。

![IMG_1212.jpg]()

以上是两个月来做的工作,很不容易,但是做成了。

这款驱动板的意义非凡,是国内第一块使用可编程逻辑器件的DRSSTC驱动板。

掌握了完全的自主知识产权。它能实现

1:SKP模式和普通DRSSTC驱动板模式硬件兼容。

2:SKP/OCD阈值调节。

3:全数字模式实现传统DR驱动功能,不需要任何RC外围处理信号。

4:peak ±20A 单路驱动能力,可轻松驱动全桥/半桥等拓扑。

5:逻辑延迟小至7nS,整板延迟小于40nS,保证理想工作。

6:完善的复位电路,保证强电磁环境下的正常工作。

——

其他的一些初始特性

1:软件灭弧限宽

2:软件灭弧锁存

这个帖子主要介绍一下这俩个月以来的研发历程。

细节慢慢补充,有问题可以在帖子后面跟,能回答的尽量回答。

觉得非常有意思,其原理在之前的帖子里已经发了。

XXXXXXXXXXXXXXXXXXXXXXXX/t/81286

鉴于需求比较清晰,所以开发起来就有了方向。

由于跳脉冲驱动模式比较特殊,也没有人用分立电路的形式设计一款合适的驱动电路。

所以我便萌生了使用可编程逻辑器件来实现驱动的意向,其实skp模式的需求主要可以分化如下。

1:保持DR4-1.3b系列具有的一切特性,同步灭弧、关断。

2:拥有过流后,发生一次跳脉冲而非直接关断的新特性。

——

由于谐振驱动电路的特性,所以一切操作都必须遵循过零点切换。

了解到以上特征,我年前花了两天时间,用verilog写了几百行代码。

初步实现了DR4-1.3b移植到CPLD上,这也算是一个里程碑。

可以看到综合出来的这一段RTL一共可以分为四个模块。

前两个模块是对灭弧和反馈信号做同步,最后一个模块是能够在发生skp的时候。

交替关断,均摊发热量。

寥寥四个模块,就构成了skp的基本功能形式。图中看出,skp功能已经被实现。

但是依然存在一些问题。

其中核心代码分享如下

<code class="lang-">module Edge_Trrig//OK Over_INT Enable/1 ( Over_IN,FedA,FedB,Control_Int,Enable ); input Over_IN,FedA,FedB,Enable; output Control_Int; /* wire LineA,LineB,LineC; */ wire Q1,Q2,Over_IN_N; Dflop dff1 ( .clk(FedB), .rst_n(Enable), .din(Over_IN), .dout(Q1) ); Dflop dff2 ( .clk(FedA), .rst_n(Enable), .din(Over_IN), .dout(Q2) ); /* assign LineA = (!(FedA&(!Q2))); assign LineB = (!(Q2&FedA)); assign LineC = (!(Q1&LineA)); assign Control_Int=LineB&LineC&Enable; That it is Hardware logic */ assign Control_Int = Enable&((!(Q1&(!(FedA&(!Q2)))))&(!(FedA&Q2))); endmodule</code>

这个模块产生了一个以FB信号更新的上升、下降沿D触发器。

实现基本skp功能。

——

篇幅有限 ——时光如流水,无数个昼夜,三个月之后->

——

它更新到了V2.3beta

RTL综合如下。

最终功能全部完善,能够完全不要模拟外围实现逻辑功能。

代码也比当时翻了三倍,但一切的努力都没有白费。

在高压局和工业局各位同志热心的帮助下,这款skp驱动板终于以硬件的形式呈现在我的面前。

这里要特别感谢袁局(review) 、NPK(logo)、虎哥(suggest)和我的妹子(logo)provide。

以上是两个月来做的工作,很不容易,但是做成了。

这款驱动板的意义非凡,是国内第一块使用可编程逻辑器件的DRSSTC驱动板。

掌握了完全的自主知识产权。它能实现

1:SKP模式和普通DRSSTC驱动板模式硬件兼容。

2:SKP/OCD阈值调节。

3:全数字模式实现传统DR驱动功能,不需要任何RC外围处理信号。

4:peak ±20A 单路驱动能力,可轻松驱动全桥/半桥等拓扑。

5:逻辑延迟小至7nS,整板延迟小于40nS,保证理想工作。

6:完善的复位电路,保证强电磁环境下的正常工作。

——

其他的一些初始特性

1:软件灭弧限宽

2:软件灭弧锁存

这个帖子主要介绍一下这俩个月以来的研发历程。

细节慢慢补充,有问题可以在帖子后面跟,能回答的尽量回答。

[修改于 7年9个月前 - 2017/03/24 00:16:09]

恭喜,山东人民发来贺电!

玩了几年DR的同志们终于又有新玩具可以搞了

玩了几年DR的同志们终于又有新玩具可以搞了

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。

牛逼,又是一个质的飞越,顶顶顶........,期待能用上你的产品

引用

加载评论中,请稍候...

200字以内,仅用于支线交流,主线讨论请采用回复功能。